易灵思FPGA-项目设计指南一

原理背景

我们以往的做工程的是习惯,先完成代码端的任务,工程不大,功能不复杂的情况下,甚至都不会做仿真和约束;

然后在板子上实际抓波形,看现象来判断,定位问题,修Bug;

这种操作在移植易灵思平台的过程中,往往会事倍功半:

易灵思FPGA 芯片在设计之初,采用了 硬件接口(GPIO,JTAG,PLL) 和 内核逻辑(Core)分开设计的思路,所以在切换之初会有些许的不适应,但这样的操作好处是,符合自上向下设计的思路,当在Interface Designer界面配置完所以的接口没问题后,EDA工具会根据分配的管脚,自动生成对应的顶层文件;

模块实例

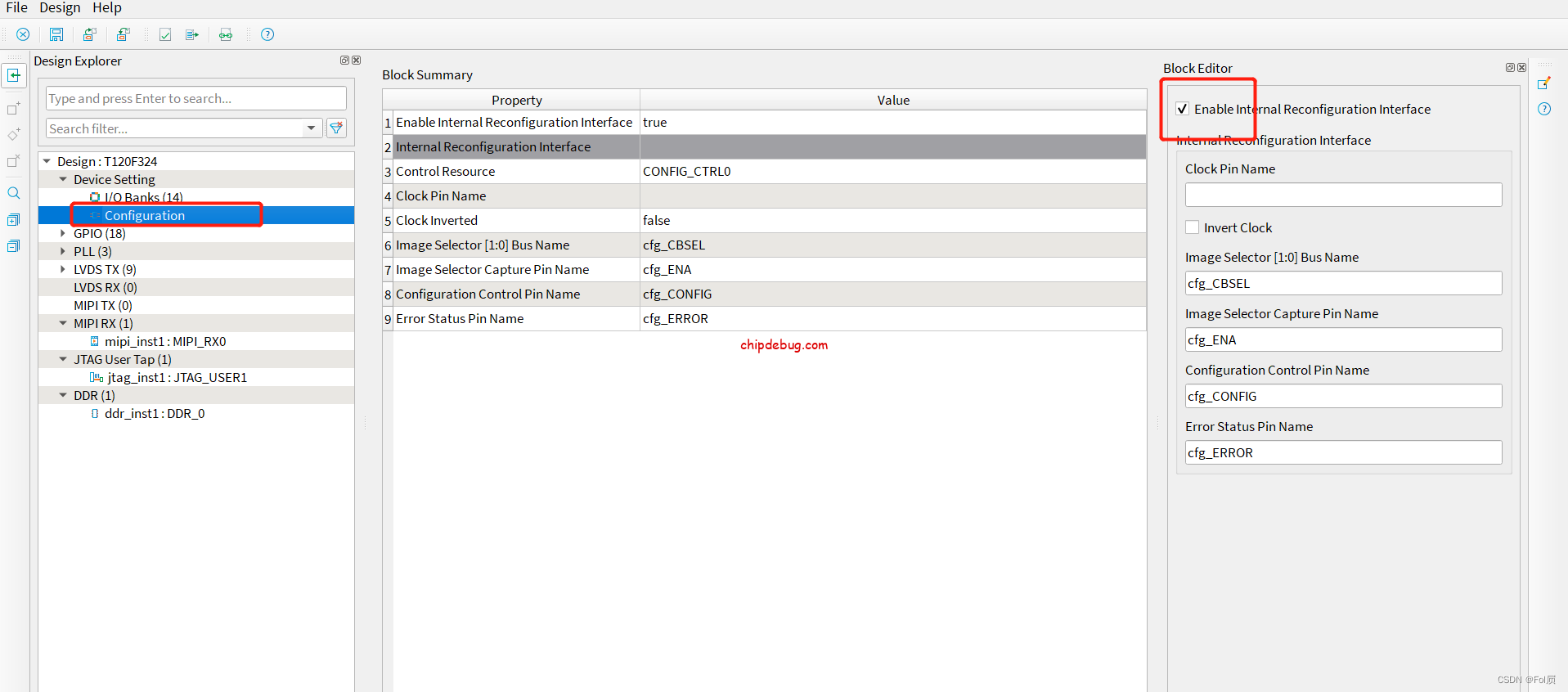

在分配管脚的界面,如下图,拿T120F324C4 芯片为例,参考一官方的demo,设置一些需要的信号;

Device Settings

设置不同bank的电压

设置是否使用内部重配置 以及 对应的信号;

GPIO

在此模块里面 ,可以添加 input output pll_in inpout 等类型;

PLL

笔者有其他文章专门描述此功能具体用法,不多赘述

LVDS-TX

根据inout分配,管脚

LVDS-RX

同理,唯一需要注意的是 RX信号 随路时钟的来源;

MIPI-RX

和TX 同理

MIPI-TX

一代的芯片MIPI是固定管脚 ,所以选择对应的资源就行;然后根据手册 给对应信号时序就行

JTAG User Tap

硬核Jtag资源,共有4个意味着 外部可以同时连4个调试口,当然一般默认选一个就够了;

**DDR **

Trion ddr 是硬核 ,和mipi 一样 选想使能的资源就行 ,只有到信号叫才链接信号,前面的行列速度等都是选择参数就行

例化顶层和做时序约束

保存设置 检查是否有错误 关联硬件 对应如图三个设置出现底部的done信号后

在对应工程的outflow 文件夹 底下 会自动生成一个 _template.v 文件;这个就是你整个工程的顶层了 ,而且确保和硬件关联的一模一样,没有问题;

在outflow 文件夹下 会有一个sdc约束文件,这个是EDA工具根据硬件配置自动生成的 ,当你选好芯片的模型时,逻辑层的时序模型就已经是确定的了;

针对端口的约束 ,某一IO寄存器的约束 ,需要在跑完结果后根据时序报告手动计算 ,这个过程是通用的;后面会出一篇针对易灵思时序约束的操作指南 ;

不过,刚开始 用户可以直接复制pt.sdc粘贴到自己的SDC文件内 ,非常便捷,无需动脑;

强调

所有的项目

一定要先设置 Interface Designer, 因为会帮用户规避

硬件画原理图 引脚不能使用,时钟信号连错,bank电压不一致,

设计代码 管脚少连多练 信号不对应等诸多问题;

没有回复内容