软件设计部分

1. DDR的硬核里有自动校准和OCT设置;

LPDDR最低可以跑100M,DDR最低可以跑200M;

VCC25A_MIPI的电流300mA的小LDO就够了;

如果用了DDR,BR0这个锁相环只能输出CLK_OUT0和CLK_OUT1;

不建议br0_clock1做为其它PLL的输入参考时钟,是因为DDR对时钟要求比较高,最好单独使用;只是将 BR0_CLOCK1拉出来 级连到其它锁相环,给逻辑用,也可以这么操作;级联不会使抖动变大,只是会增加delay,不过不用考虑DDR时钟和其他时钟的相位;

2. CBUS和CBSEL是调用FPGA内部重配置功能的,不用可以悬空;可以不用接1k的下拉电阻,直接接地,因为本身LVCMOS的输入阻抗就不小,接电阻,主要是起到限流的作用;

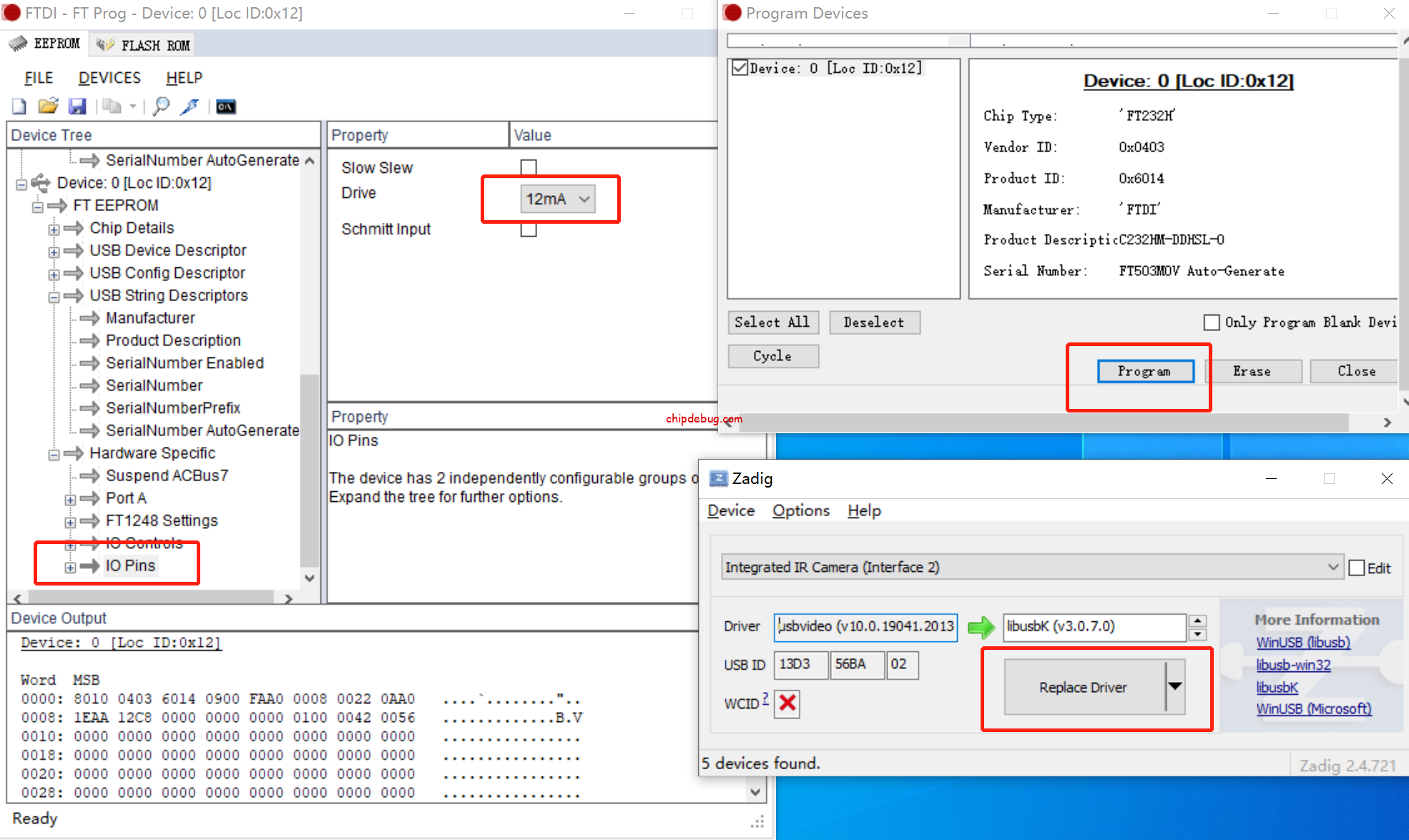

C232HM电缆的长了造成的驱动不足,会出现以下现象,觉得有碍观瞻的话,可以用FT_prog把驱动改大会有改善;

1.彻底卸载C232HM驱动

2.拔插C232HM

3.FT_prog里面找到C232HM的配置项

4.找到IO驱动的配置项,修改为8mA或者更多

5.编程电缆里的eeprom后再替换回对应的驱动。

3. Bootloader是直接初始化到OCR(on chip ram)里的,不需要放flash,app放flash,fpga启动以后,riscv直接运行ocr初始化好了的bootloader,bootloader完成flash到ddrram的搬运,然后从ddr开始执行,boot.bin用script里的脚本,生成ocr初始化的五个初始化文件,替换FPGA工程根目录下对应的bin文件,编译fpga工程即可(boot.bin要用adk里面的script的python命令,分割转化成FPGA的初始化文件),将这些转换分割好的bin放到工程根目录,编译工程就行了;

source文件夹底下有5个bin文件, 有一个是寄存器的初始化文件,四个是ocr初始化文件,因为对软件来说有short是8位,int是16位,long是32位,所以存储需要支持所有的长度 在物理上对应就必须是四个的独立的8位宽;

单独烧写APP 底下的bin转HEX 文件可能会有错,应该把FPGA的bitstream和app合并以后一起烧进去;

ERROR: Flash verify unsuccessful… mismatch found

这个错误可以忽略,其实是烧进去了,因为不是FPGA本身的内容,软件校验报错而已,app运行正常;

4. 目前的riscv是用spinal HDL和Scala来生成写的;

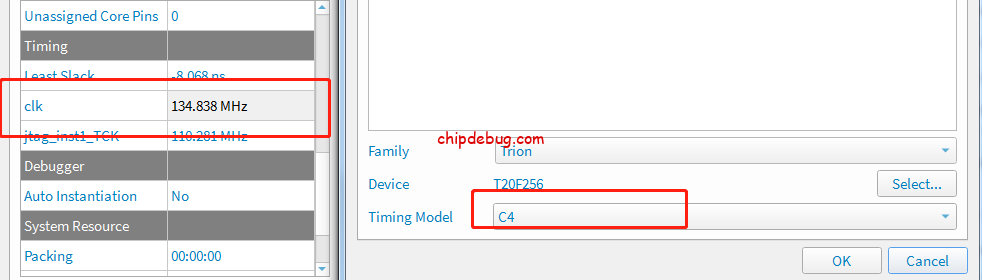

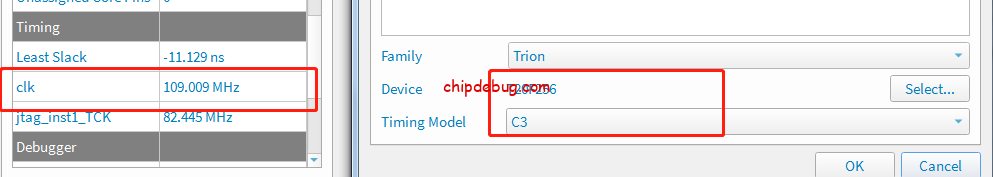

5. 器件速度的对比,以T20为例,C3,C4,I4的具体最大主频取决于代码和工程,不过总体来说,速度4是比速度3高出20%左右;

6. 在代码设计的时候 ,复位引脚如果不弱上拉,可能会悬空 ,代码启动不来;

7. 如果INOUT管脚的EN管脚设置为0,那相当于对外部接口做了高阻;

硬件设计部分

1. 实际板子设计的时候,有时候会为了省下板子上的面积,会考虑JTAG桥的方式间接下载hex ,这样可以少点下载口和连线,弊端是下载时间变的冗长,而且下载过程增加了一道手续;

所以这是一个设计选择问题:

加一个很小的座子链接flash和fpga,增加Active模式(记得加Reset);

2. 在配置flash时候,FPGA的管脚CDONE, SS_N,TEST_N,CSI必须上拉,推荐阻值10K,而CCK,CDI0,CDI1可以省去;而JTAG的TDI,TMS必须上拉,TMS=1 TDI=1 连续几个周期,就是JTAG状态机复位状态,上拉可以防止芯片意外进入JTAG状态;TDO,TCK上拉电阻可以省去;

在对没用的GPIO管脚在处理时候,布板面积有限的情况下,一般规范的做法是将5个以下相同的上下拉接到同一个电阻再到电源或者地,用的管脚这么搞就短路了;

在设计ddr的过程中,建议使用专用芯片提供的的VTT和Vref,目前还没有验证不加专用芯片和VTT电路,使用电阻分压;

3. REF_RES LVDS参考电阻 12 kΩ 是必须要的;

4. 硬件上只有一个硬JTAG,但是对内核来说可以多接口复用;

5. bank1的电压是3.3V 多以针对复位管脚,2.63V以上的POR芯片复位门槛电压都可以;

6. 一般的晶振50ppm就可以,现在的普通晶振都有25ppm

7. 如果需要加FTDI芯片,支持FT232H,FT2232H,FT4232H

没有回复内容