Cache Coherent Interconnect for Accelerators (CCIX) 是指由一个新的行业标准机构 – CCIX Consortium 开发的一组规范。CCIX 的驱动因素是需要比当前可用技术更快的互连,以及缓存一致性,允许更快地访问异构多处理器系统中的内存。出于这个原因,该联盟的工作重点是使硬件加速器能够以缓存一致的方式使用与多个处理器共享的内存。本文介绍了 CCIX 标准及其对高性能应用程序(例如机器学习、网络处理、存储卸载和内存数据库)的主要优势。

什么是缓存一致性?

当多个 CPU 共享一个公共内存空间时,它们会通过传达该内存的缓存和/或可缓存状态来获得性能。通过这种方式,每个 CPU 都可以安全地处理公共数据集的一部分,而无需使用(慢速)软件信号量来控制访问。如果 CPU A 缓存了一块内存,它可以确保 CPU B 不会修改相同的内存空间或使用过时的数据副本。CCIX 扩展了这种通信,因此 CPU 以外的代理可以参与,这使硬件加速器能够获得相同的好处。CCIX 的一致性协议也是独立于供应商的,因此 CPU、GPU 和其他加速器都可以平等参与,没有繁重的许可限制。

为了更好地理解缓存一致性,让我们研究一下现在被称为 MESI 的一段时间内常用的一致性协议。首字母缩略词 MESI 指的是系统中每个缓存行的四种可能状态:Modified 、 E exclusive、Shared 或I无效。修改意味着缓存行仅存储在当前缓存中,并且与主内存中的数据不同(缓存用语中的“脏”)。任何其他试图从系统中某处标记为已修改的地址读取的代理都将导致缓存(其中包含该地址的修改数据)在读取可能继续之前将数据写回主存储器。独占缓存行也仅存储在当前缓存中,但它与主内存中的数据匹配(缓存用语中的“干净”)。如果拥有该缓存行的代理对其进行更改,则状态将切换为独占。共享缓存行也像独占缓存行一样“干净”,但它也可能存在于系统中的其他缓存中(它也将处于共享状态)。最后,无效的缓存行正是它听起来的样子——未使用或不再有效的缓存行。显然,这样一个系统中的各种高速缓存必须相互通信多条信息。它们必须支持对来自其他代理的总线事务的侦听或监视,以确定它们的缓存状态何时需要更改,并且它们必须有某种方式将状态更改传达给系统中的其他缓存。

CCIX 协议规范定义了一组缓存状态和相关的消息和机制来完成这种相同的一般类型的行为。虽然只有 CCIX 联盟成员才能获得完整的详细信息,但本文将对协议规范进行高级概述。

为什么选择 CCIX 来实现缓存一致性?

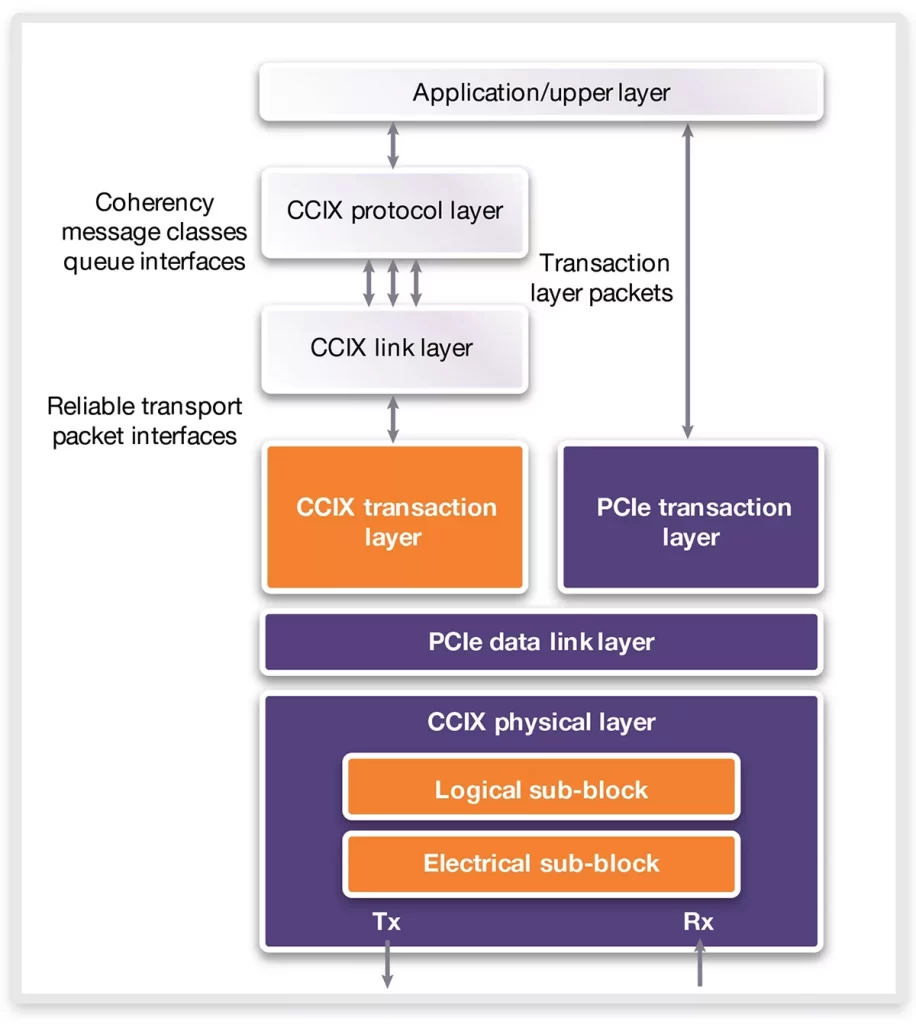

CCIX 规范的最大优势之一是它建立在 PCI® Express 规范之上。CCIX 的一致性协议可以通过 PCI Express 链路进行传输,只需很少或无需修改。如图 1 所示,现有的 PCI Express 控制器实现可以通过逻辑进行扩展,以实现 CCIX 事务层。CCIX 事务层负责承载一致性消息,而块——CCIX 协议层和链路层——负责实现一致性协议本身并对其进行操作。这些模块需要与内部片上系统 (SoC) 逻辑紧密集成以进行缓存,并且可能非常特定于该 SoC 上使用的特定架构。

图 1:CCIX 规范利用 PCI Express 协议实现 CCIX 事务层

超越 16GT/s

如前所述,CCIX 最大的吸引力之一是它与 PCI Express 的兼容性,事实上 CCIX 的缓存一致性协议可以通过任何运行 8GT/s 或更快的 PCI Express 链路进行传输。PCI Express 4.0 规定的最高数据速率为 16GT/s,在 16 通道链路上的总双向带宽约为 64GB/s,但 CCIX 联盟的一些成员需要更多带宽。他们确定,通过将传输速率提高到 25GT/s,CCIX 链路在相同条件下可以接近 100GB/s。这导致了称为扩展速度模式 (ESM) 的 CCIX 功能。由于 PCI Express 由不同的标准机构拥有,CCIX 联盟选择了一种巧妙的机制来允许支持 ESM 的组件和 PCI Express 组件之间的兼容性。希望相互通信的两个 CCIX 组件通过正常的 PCI Express 链路初始化过程(通常是硬件自主过程)继续到相互支持的最高 PCI Express 速度。从那时起,在主机系统上运行的软件可以询问特定于 CCIX 的配置寄存器,并确定两个组件是否支持 ESM,如果支持,则确定它们支持的最高速度。然后,该软件对两个组件上的其他 CCIX 特定寄存器进行编程,以将 PCI Express 链接速度映射到 CCIX ESM 链接速度。从那时起,链路协商将针对 CCIX ESM 速度,因此通过强制重新训练链路,这两个组件现在可以以 25GT/s 的速度进行通信。

结论

寻求高速缓存一致性互连的设计人员可以通过相对简单的迁移路径从当今占主导地位的 PCI Express 接口迁移,他们应该考虑将 CCIX 用于他们的下一个高性能 SoC。Synopsys 完整的CCIX IP 解决方案基于经过硅验证的 PCI Express 4.0 DesignWare® IP,该 IP 在 1,500 多个设计中得到验证并以数十亿个单位出货,可实现高速缓存一致性和高达 25 Gbps 的速度。作为 CCIX 联盟和 PCI-SIG 的活跃成员,新思科技将继续在 CCIX、PCI Express 和相关技术方面进行创新,以确保生态系统满足其对数据密集型云计算应用程序的高性能连接要求。

没有回复内容