《适用于FPGA和SOC的UlteraFast设计方法指南》(UG949)

《Vivado Design Suite 用户指南:设计分析与收敛技巧》(UG906)

《Vivado Design Suite 用户指南:使用约束》(UG903)

《Vivado Design Suite Tcl 命令参考指南》(UG835)

约束文件读取顺序,工程模式下,使用reorder_files的TCL命令来修改约束文件的顺序

时序约束总体应该遵循的顺序:

## Timing Assertions Section

# Primary clocks

# Virtual clocks

# Generated clocks

# Delay for external MMCM/PLL feedback loop

# Clock Uncertainty and Jitter

# Input and output delay constraints

# Clock Groups and Clock False Paths

## Timing Exceptions Section

# False Paths

# Max Delay / Min Delay

# Multicycle Paths

# Case Analysis

# Disable Timing

使用多个XDC文件时,必须特别留意时钟定义,并确认从属关系排序是否正确

综合约束使用的名称必须来自细化的网表(最好是端口和时序单元)。某些 RTL 信号会在细化过程中消失,并且无法为其赋予 XDC 约束。此外,由于细化后执行的各种最优化,信号线或逻辑单元将合并到各种技术原语(例如,LUT 或 DSP 块)中。要了解详细设计对象的名称,单击 Flow Navigator 中的Open Elaborated Design,然后浏览您感兴趣的层级。

所有经细化的网表对象或层级均可通过使用 DONT_TOUCH、KEEP、KEEP_HIERARCHY 或 MARK_DEBUG 约束来保留,但存在时序或面积 QoR 劣化的风险。

最后,某些约束可能存在冲突而不被综合所认可。例如,如果在跨多个层级的网表上设置 MAX_FANOUT 属性,并且使用 DONT_TOUCH 保留部分层级,那么将限制或完全阻止扇出最优化。

定义时序约束四个步骤:

前 2 个步骤与时序断言有效有关,期间将从时钟波形和 I/O 延迟约束中衍生出默认时序路径要求。

在第 3 个步骤中,将对至少共享 1 条逻辑路径的异步或专属时钟域之间的关系进行审核。根据关系的性质,可输入时钟组或伪路径约束以忽略这些路径上的时序分析。

最后一个步骤对应于时序例外,设计人员可在此判定如何更改默认时序路径要求,包括利用特定约束来忽略、放宽或收紧时序要求。

定义时钟约束

时钟必须首先完成定义,方可供其它约束使用。时序约束创建流程的第一步是明确必须定义哪些时钟,以及这些时钟必须定义为“primary clock”(基准时钟)还是“generated clock”(生成时钟)。使用特定名称定义时钟(-name 选项)时,必须验证该时钟名称未被任何其它时钟约束或现有自动生成时钟占用。赛灵思建议避免覆盖时钟定义。

在设计中可通过“Clock Networks”(时钟网络)报告和“Check Timing”(检查时序)报告来识别未约束的时钟源。

检查设计是否正确约束

在查看时序结果是否存在违例之前,应确保设计中的每个同步端点都已正确约束。

运行 check_timing 可识别未约束的路径。此命令可单独运行,但也可随 report_timing_summary 一起运行。此外,report_timing_summary 还包含“Unconstrained Paths”(未约束的路径)部分,其中已定义的源或目标时序时钟会列出不含时序要求的 N 条逻辑路径。N 由 -max_path 选项控制。

对设计实现完全约束后,请运行 report_methodology 命令并复查 TIMING 和 XDC 检查,以识别非最优化约束,此类约束可能导致时序分析不完全准确,并导致硬件中时序裕度 (timing margin) 发生变化。要识别并纠正不现实的目标时钟频率或者建立路径要求,请使用 report_qor_assessment 命令。

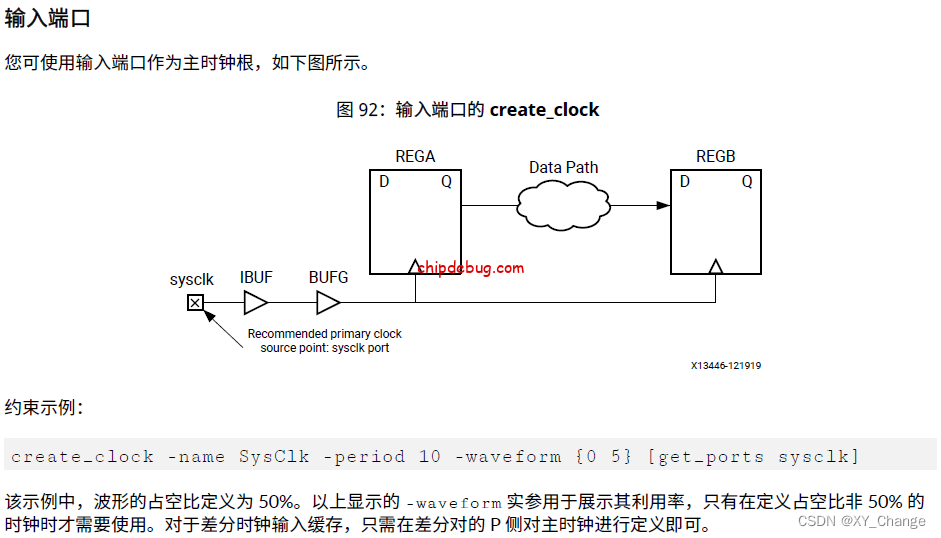

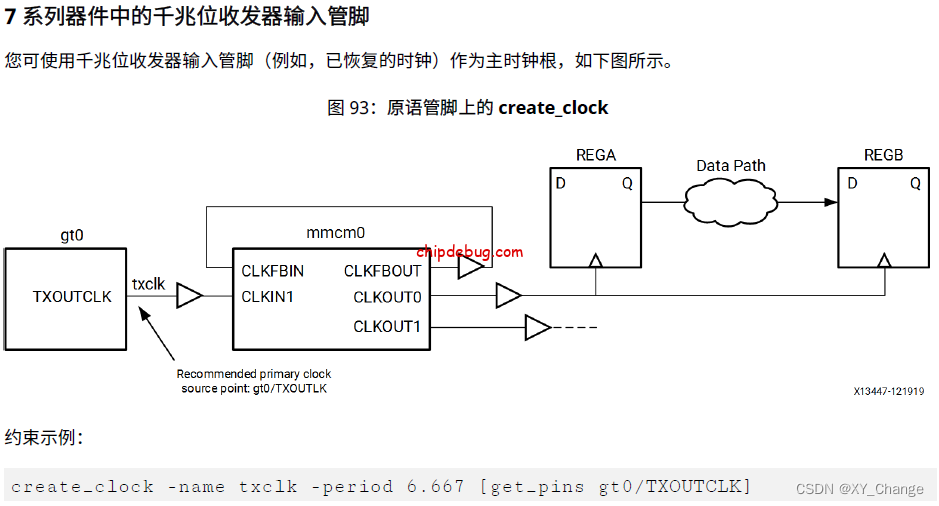

创建基准时钟(主时钟)

基准时钟是指用于为设计定义时序参考的时钟,而时序引擎可利用基准时钟衍生出时序路径要求以及与其它时钟的相位关系。主时钟插入延迟的计算范围是从时钟源点(用于定义时钟的驱动管脚/端口)到时序单元(作为时钟扇出目标)的时钟管脚。

因此,重要的是在对应于设计边界的对象上定义基准时钟,以便准确计算其延迟并间接计算其偏差。

注意,不要用某些硬件原语的输出管脚创建基准时钟或者在一个时钟的扇出中使用create_clock。

在基准时钟传递扇出中不应定义另外 1 个基准时钟,因为这种情况不但不符合任何硬件现实,还会妨碍完整的时钟插入延迟计算,从而阻碍正确的时序分析。如果发生任何这种情况,必须重新修改并修正约束。

下图显示的示例中,时钟 clk1 是在时钟 clk0 的传递扇出中定义的。时钟 clk1 会从 BUFG1 输出开始覆盖此输出处所定义的 clk0。因此,由于 clk0 与 clk1 之间歪斜突变无效导致 REGA 与 REGB 之间的时序分析并不准确。

创建生成时钟

生成时钟 (generated clock) 是从称为主时钟 (master clock) 的另一个现有时钟衍生的。它通常用于描述逻辑块对主时钟执行的波形变换。由于生成时钟定义取决于主时钟特性,因此必须首先定义主时钟。为显式定义生成时钟,必须使用 create_generated_clock 命令。

自动衍生时钟

大部分生成时钟都是由 Vivado 时序引擎自动衍生的,该引擎可识别时钟修改块 (CMB) 及其对主时钟执行的变换。

在赛灵思 7 系列器件中,CMB 包括:

- MMCM*/PLL*

- BUFR

- PHASER*

在赛灵思 UltraScale 系列器件中,CMB 包括:

- MMCM*/PLL*

- BUFG_GT/BUFGCE_DIV

- GT*_COMMON/GT*_CHANNEL/IBUFDS_GTE3

- BITSLICE_CONTROL/RX*_BITSLICE

- ISERDESE3

对于时钟树上的任何其它组合单元而言,时序时钟可通过这些单元进行传输,且无需在输出端重新定义,除非此类单元已进行波形变换。通常应尽可能依靠自动衍生机制,因为就定义可对应于实际硬件行为的生成时钟来说,这是最安全的方法。

如果您认为 Vivado Design Suite 时序引擎所选的自动衍生时钟名称不合适,那么可以使用

create_generated_clock 命令(不指定波形变换)强制输入自己选择的名称。该约束应刚好位于约束文件中定义

主时钟的约束之后。例如,如果由 MMCM 实例生成的时钟默认名称为 net0,那么您可添加以下约束来强制输入自己的名称(在给定示例中,此名称为 fftClk)。

create_generated_clock -name fftClk [get_pins mmcm_i/CLKOUT0]

用户定义的生成时钟

定义所有主时钟后,可使用“时钟网络 (Clock Networks)”或“检查时序 (Check Timing)”(no_clock) 报告来识别时

钟树中不含时序时钟的部分,并定义相应的生成时钟。

有时要理解逻辑椎对主时钟所执行的变换并不容易。在此情况下,必须采用最保守的约束。例如,源管脚是时序单元输出。主时钟至少除以 2,因此,正确的约束应如下示例所示:

create_generated_clock -name clkDiv2 -divide_by 2

-source [get_pins fd/C] [get_pins fd/Q]

最后,如果设计包含锁存器,那么时序时钟还需要连接到锁存器门控管脚,并且如果缺少约束,则将由“检查时序

(Check Timing)”(no_clock) 来报告锁存器门控管脚。您可遵循上述示例来定义这些时钟。

主时钟与生成时钟间的路径

与主时钟不同,生成时钟必须在其主时钟的传递扇出中进行定义,这样时序引擎才能精确计算其插入延迟。不遵守此原则将导致时序分析错误,而且很有可能导致时序裕量计算无效。例如,在下图中,gen_clk_reg/Q 用作为下一个触发器 (q_reg) 的时钟,并且它还位于主时钟 c1 的扇出椎中。因此,gen_clk_reg/Q 应包含

create_generated_clock 而不是 create_clock。

create_generated_clock -name GC1 -source [get_pins gen_clk_reg/C] -divide_by 2

[get_pins gen_clk_reg/Q]

验证时钟定义和覆盖范围

在定义并应用所有设计时钟后,即可使用 report_clocks 命令验证每个时钟的波形以及主时钟和生成时钟

之间的关系:

此外,您还可验证所有内部时序路径都被至少 1 个时钟所覆盖。“检查时序 (Check Timing)”报告为此提供了两项检

查:

- no_clock:报告已定义的时钟无法连接到的任何活动时钟管脚。

- unconstrained_internal_endpoint:如果某些时序单元具有与时钟相关的时序检查但尚未定义时钟,则报告此类时序单元的所有数据输入管脚。

如果两项检查都返回 0,说明时序分析覆盖范围广。

或者,还可运行 XDC 和“时序方法 (Timing Methodology)”检查来验证在建议的网表对象上是否已定义所有时钟,同

时避免造成任何约束冲突或不准确的时序分析情境。

请使用以下命令来运行这些检查:

report_methodology -checks [get_methodology_checks {TIMING-* XDC*}]

调整时钟特性

定义时钟及其波形后,下一步是输入与噪声或不确定性建模相关的所有信息。XDC 语言用于将抖动和相位误差相关的不确定性与偏差和延迟建模相关的不确定性加以区分。

抖动

对于抖动,最好使用 Vivado Design Suite 所使用的默认值。您可按如下方式修改默认计算:

- 如果主时钟进入器件时随机抖动大于 0,请使用 set_input_jitter 命令指定峰值间抖动值(以纳秒 (ns) 为单

位)。 - 如果器件电源有噪声,请使用 set_system_jitter 调整全局抖动。赛灵思不建议增大默认系统抖动值。

对于生成时钟,抖动源自主时钟和时钟修改块的特性。用户不需要调整这些数字。

其他不确定性问题

如果需要在某个时钟的时序路径上或 2 个时钟之间的时序路径上添加额外裕度,必须使用

set_clock_uncertainty 命令。这也是对部分设计进行过度优化而不必修改实际时钟沿和总体时钟关系的最佳且最

安全的途径。用户定义的时钟不确定性是在 Vivado 工具计算所得抖动的基础上附加的,可为建立时间和保持时间分析单独指定此不确定性。

例如,设计时钟 clk0 的所有时钟间路径上的裕度需收紧,幅度为 500 ps,以使设计承受建立时间和保持时间的噪声

能力更强:

set_clock_uncertainty -from clk0 -to clk0 0.500

如果您在 2 个时钟之间指定额外的不确定性,那么必须应用双向约束(假定数据流为双向)。以下示例演示了如何在clk0 和 clk1 之间仅针对建立时间将不确定性增加 250 ps。

set_clock_uncertainty -from clk0 -to clk1 0.250 -setup

set_clock_uncertainty -from clk1 -to clk0 0.250 -setup

时钟源位置的时钟时延

可使用含 -source 选项的 set_clock_latency 命令在时钟源处对时钟时延进行建模。该方法在两种情况下有用:

- 用于在器件外部指定与输入和输出延迟约束无关时钟延迟传输。

- 用于对非关联 (OOC) 编译器件块所使用的时钟内部传输时延进行建模。在此类编译流程中,不含完整时钟树的描述,因此块外部的最小和最大工作条件之间的差异无法自动进行计算,必须手动建模。

此约束仅限高级用户使用,因为它通常难以提供有效的时延值。

MMCM 或 PLL 外部反馈回路延迟

当连接 MMCM 或 PLL 反馈回路以便补偿开发板延迟(而非内部时钟插入延迟)时,必须使用

set_external_delay 命令指定最佳和最差延迟情况下器件外部的延迟。不指定此延迟会导致与 MMCM 或 PLL 关

联的 I/O 时序分析变得无关紧要,并且可能导致无法实现时序收敛。此外,使用外部补偿时,必须相应调整输入和输

出延迟约束,而不只是考量正常情况下开发板上的时钟走线延迟。

没有回复内容