.0AXI GPIO

第一部分

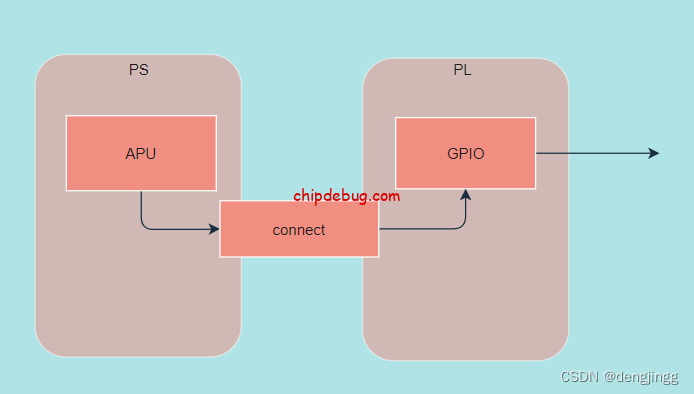

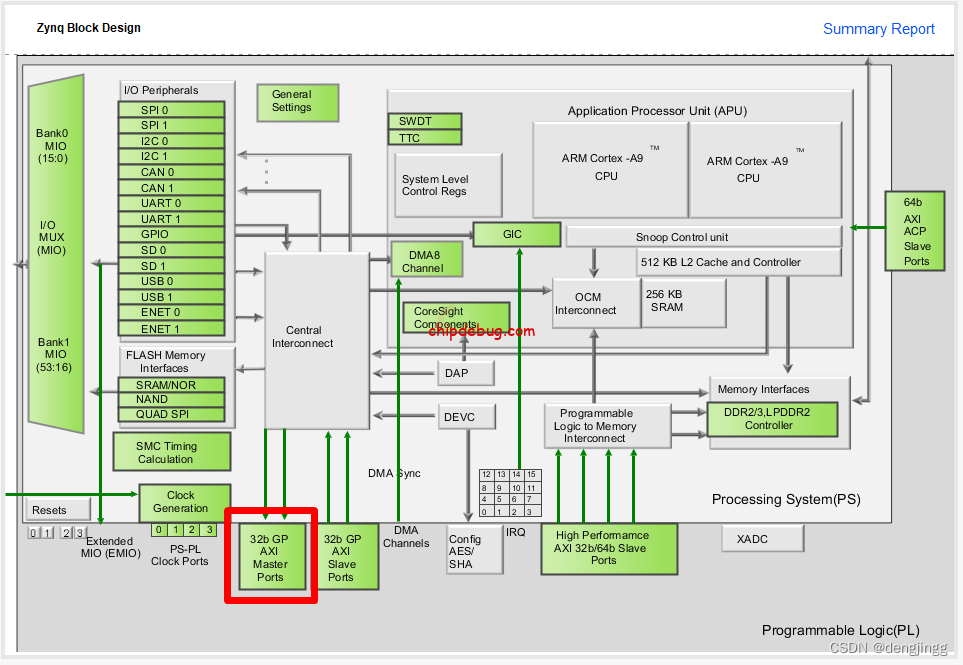

PS 和 PL之间的通讯有一个接口称为AXI。AXI总线具体的内容这边不去深究,可以理解为一种特殊协议的通讯方式。

AXI GPIO是什么意思?

PL是FPGA它可以做成任何你想要的东西,做一个GPIO外设当然是可以的。

如上图所示,假设我们用FPGA 设计了一个GPIO外设,它可以通过引脚进行电平的输入和输出。

这个时候PS端的APU需要使用GPIO,通常就是GPIO的读写操作。这个事件这个需要数据通信,上图所示有个connect的模块横跨PS,PL,用于数据的传输,没错AXI就是这个connect。这里我们把AXI单纯的看做一个有特殊协议的通信线路,暂时不去关系实现方式。

第二部分

什么是GPIO,这个问题好像非常简单,但是好像也不简单。为了寻求这个答案,可以看一下MCU的GPIO结构

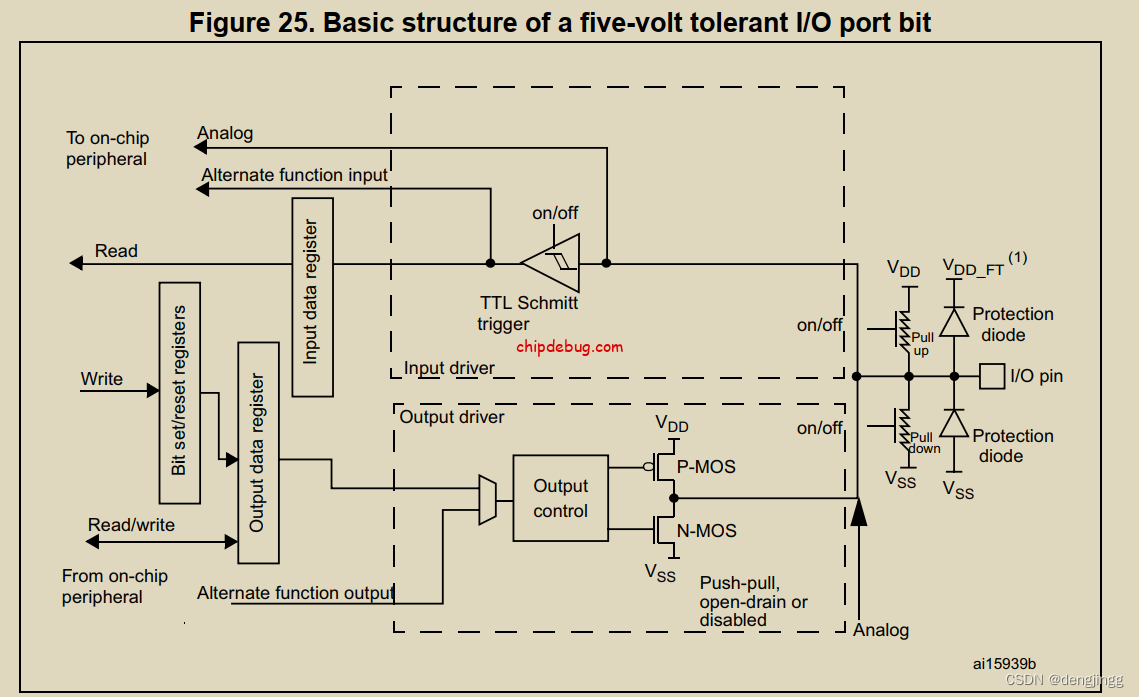

打开STM32F407(Cortex M4)手册的GPIO章节

上图所示,最右边是最后芯片引出的物理引脚。最左边是GPIO模块对外的接口。提供读写操作。

那么我们如果要做一个GPIO外设就需要物理引脚和读写接口。

那么物理引脚可以想到FPGA开发中的引脚分配。这里会问不是有EMIO了吗为啥还要AXI GPIO

1.EMIO本质上是硬核

2.AXI GPIO是真正的软核FPGA开发

那么读写接口就是第一部分所说的AXI接口。

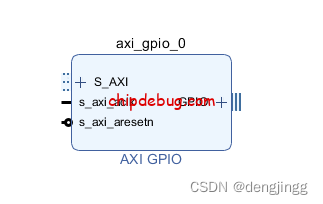

那么GPIO具体什么实现呢,xilinx 官方把GPIO如何实现已经做好了,封装成AXI GPIO IP。我们直接调用即可。

Create Block design->添加IP ->AXI GPIO

在AXI IP官方手册中

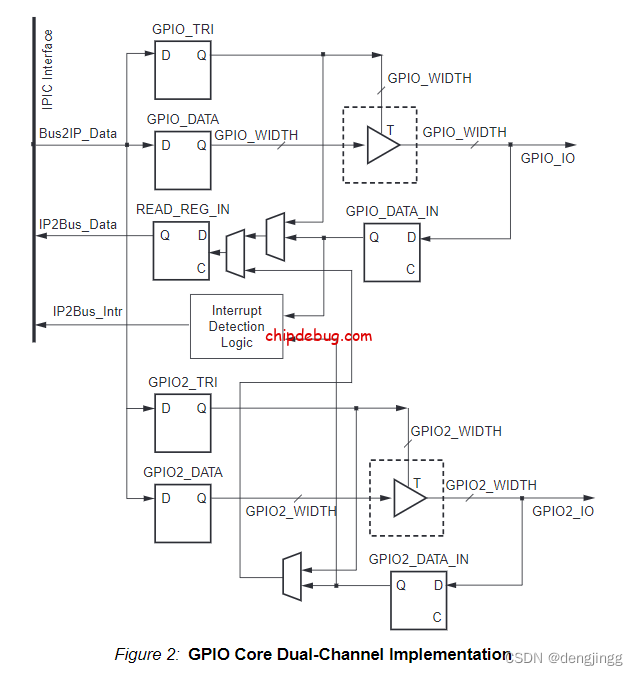

AXI GPIO de 构成如上图所示,

1.AXI Interface 用于AXI中线的通讯

2.interrupt Module 检测GPIO模块的Read信号,判断是否发生中断,送入专用的信号线IP2INTC.

3.GPIO Core 就是GPIO 外设了

GPIO 具体的结构

1.GPIO 三态门的控制TRI

2.Write

3.read

还可以通过多路选择器构建两个GPIO外设。

第三部分

知道AXI GPIO是什么东西后,那么要怎么去配置

可以配置默认的输出电平和门控状态(输入还是输出)。

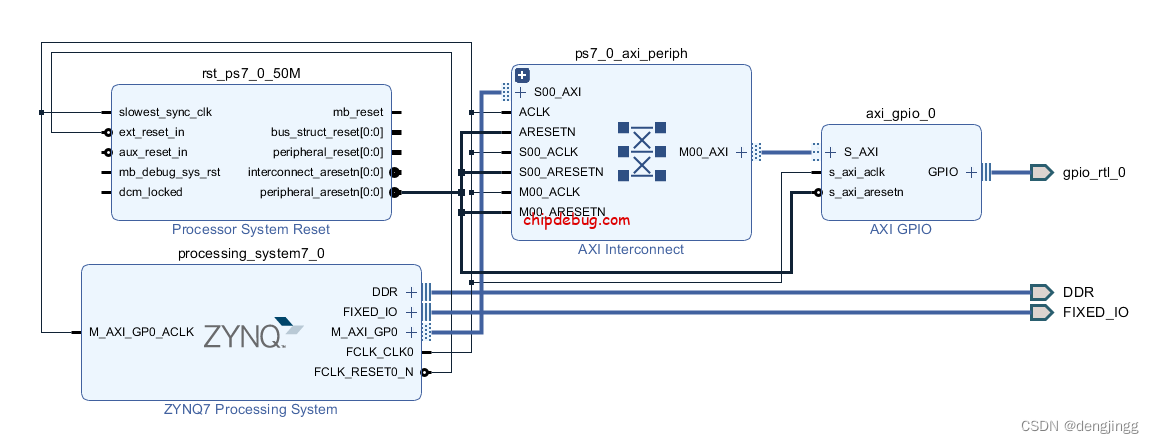

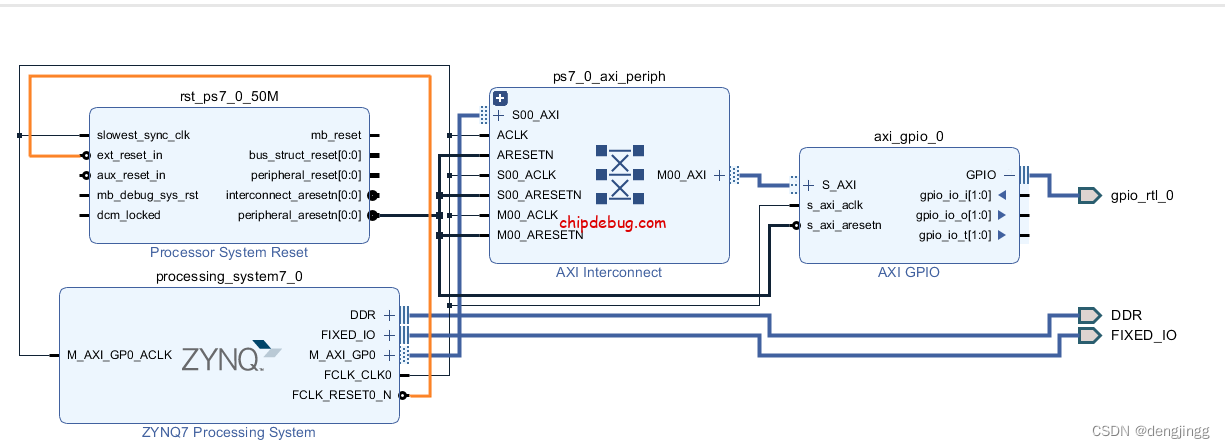

添加zynq PS 后,点击自动连接,vivado自己生成了axi interconnect和PS reset

PS的FCLK_CLK0 ,给AXI Interconnect 和AXI GPIO提供了时钟。peripheral aReastn提供了复位信号。

PS的M_AXI_GP0 和AXI Interconnect连接,PS也提供AXI时钟。

FCLK_CLK0 是PS端提供给PL端的时钟信号,供给了所有AXI 相关的所有IP。

FCLK_RESET0_N 这个信号给到processor System Reast IP ,然后通过peripheral aReastn 对AXI 互联和AXI GPIO提供复位信号。

AXI Interconnect 是一个AXI总线的连接矩阵,有点像路由器的意思

这样通过xilinx AXI GPIO IP核构建了一个 AXI 接口的GPIO模块。

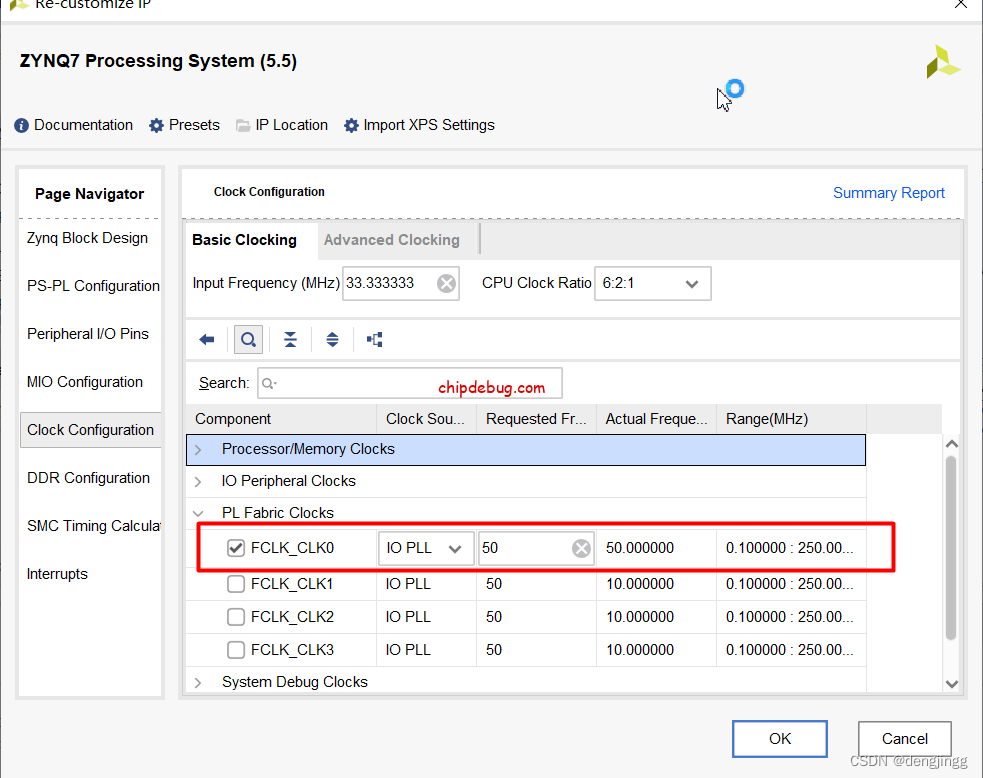

clock Configuration 设置时钟,提供给AXI和AXI GPIO

打开AXI GPIO的中断,它的中断信号属于PL中断信号,相关设置在GIC中。

如下图所示,双击GIC

打开PL -PS的中断信号,其中断号是84~91。

最后进行引脚分配

.

配置AXI GPIO的端口,生成比特流。

第四部分

AXI GPIO编程,导入官方例程。见下章

没有回复内容