什么是芯片制造的Corner以及SS/TT/FF特点?

世界上没有两片叶子是相同的,同样世界上没有两个芯片是相同的。 芯片制造是一个物理过程,存在着工艺偏差(包括掺杂浓度、扩散深度、刻蚀程度等),导致不同批次(lot)之间,同一批次不同晶圆(wafer)之间,同一晶圆不同晶片(die)之间情况都是不相同的。 从专业的角度怎么定量描述这些制造工艺带来的个体差异,于是corner的概念产生了。

一、什么是Corner?

在一片wafer上,不可能每个芯片的载流子平均漂移速度都是一样的,随着电压、温度不同,它们的特性也会不同。 把他们分类就有了PVT(Process,Voltage,Temperature) Process:工艺制造 Voltage:电压 Temperature: 温度 而Process又分为不同的corner,process corner称之为工艺角,

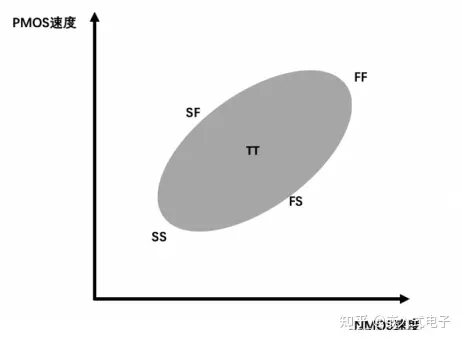

典型的5种corner,

TT:Typical N Typical P

FF:Fast N Fast P

SS:Slow N Slow P

FS:Fast N Slow P

SF:Slow N Fast P  注: SS、 TT、FF 分别是左下角的corner, 中心、右上角corner 第一个字母代表NMOS,第二个字母代表PMOS,都是针对不同浓度的N型和P型掺杂来说的。NMOS和PMOS在工艺上是独立做出来的,彼此之间不会影响,但是对于电路,NMOS和PMOS是同时工作的,会出现NMOS快的同时PMOS也快,或者慢,所以会出现FF、SS、FS、SF四种情况。通过Process注入的调整,模拟器件速度快慢,同时根据偏差大小设定不同等级的FF和SS。正常情况下大部分是TT,而以上5种corner在+/-3sigma可以覆盖约99.73%的范围,这种随机性的发生符合正态分布。

注: SS、 TT、FF 分别是左下角的corner, 中心、右上角corner 第一个字母代表NMOS,第二个字母代表PMOS,都是针对不同浓度的N型和P型掺杂来说的。NMOS和PMOS在工艺上是独立做出来的,彼此之间不会影响,但是对于电路,NMOS和PMOS是同时工作的,会出现NMOS快的同时PMOS也快,或者慢,所以会出现FF、SS、FS、SF四种情况。通过Process注入的调整,模拟器件速度快慢,同时根据偏差大小设定不同等级的FF和SS。正常情况下大部分是TT,而以上5种corner在+/-3sigma可以覆盖约99.73%的范围,这种随机性的发生符合正态分布。

二、Corner的意义

与双极晶体管不同,在不同的晶片之间以及在不同的批次之间,MOSFETs 参数变化很大。为了在一定程度上减轻电路设计任务的困难,工艺工程师们要保证器件的性能在某个范围内。如果超过这个范围,就将这颗IC报废了,通过这种方式来保证IC的良率。 传统上,提供给设计师的性能范围只适用于数字电路并以“工艺角”(Process Corners)的形式给出。其思想是:把NMOS和PMOS晶体管的速度波动范围限制在由四个角所确定的矩形内。这四个角分别是:快NFET和快PFET,慢NFET和慢PFET,快NFET和慢PFET,慢NFET和快PFET。例如,具有较薄的栅氧、较低阈值电压的晶体管,就落在快角附近。从晶片中提取与每一个角相对应的器件模型时,片上NMOS和PMOS的测试结构显示出不同的门延迟,而这些角的实际选取是为了得到可接受的成品率。因此,只有满足这些性能的指标的晶片才认为是合格的。在各种工艺角和极限温度条件下对电路进行仿真是决定成品率的基础。

三、PVT (process, voltage, temperature)

设计除了要满足上述5个corner外,还需要满足电压与温度等条件, 形成的组合称为PVT (process, voltage, temperature) 条件。电压如:1.0v+10% ,1.0v ,1.0v-10% ; 温度如:-40C, 0C 25C, 125C。 设计时设计师还常考虑找到最好最坏情况. 时序分析中将最好的条件(Best Case)定义为速度最快的情况, 而最坏的条件(Worst Case)则相反。 根据不同的仿真需要,会有不同的PVT组合。以下列举几种标准STA分析条件:

WCS (Worst Case Slow) : slow process, high temperature, lowest voltage

TYP (typical) : typical process, nominal temperature, nominal voltage

BCF (Best Case Fast ) : fast process, lowest temperature, high voltage

WCL (Worst Case @ Cold) : slow process, lowest temperature, lowest voltage

在进行功耗分析时,可能是另些组合如:

ML (Maximal Leakage ) : fast process, high temperature, high voltage

TL (typical Leakage ) : typical process, high temperature, nominal voltage

四、总结

由于芯片制造工艺的差异,会导致不同的芯片有不同的特性,为了保证芯片的良率需要对芯片制造差异的SS、FF、SF、FS、TT 5种corner进行设计保证和验证。 芯片标称的最大工作频率一般都是以SS/TT这个标准来标称的,

1. 根据正态分布规律,大部分芯片是高于SS/TT的,这也是为什么以前的电脑CPU可以超频的原因

2. 芯片确实由于工艺差异,不能达到SS/TT的,降低芯片性能要求也可以使用。这也是为什么同样的芯片,通过筛选后有的当工业级销售,有的当消费级销售;或者降低标称频率等性能后,当作低端芯片销售。

芯片测试相关术语解释(CP、FT、WAT)

CP测试

英文全称Circuit Probing、Chip Probing,也称为晶圆测试,测试对象是针对整片wafer中的每一个Die,目的是确保整片wafer中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。可以用来检测fab厂制造的工艺水平。probe, 探查,查看

CP的难点是如何在最短的时间内挑出坏的die,修补die。

常用到的设备有测试机(IC Tester)、探针台(Prober)以及测试机与探针卡之间的接口(Mechanical Interface)

基本原理是探针加信号激励给pad,然后测试功能。

a.测试对象,wafer芯片,还未封装;

b. 测试目的,筛选,然后决定是否封装。可以节省封装成本(MPW阶段,不需要;fullmask量产阶段,才有节省成本的意义)。

c. 需要保证:基本功能成功即可,主要是机台测试成本高。高速信号不可能,最大支持100~400Mbps;高精度的也不行。总之,通常CP测试,仅仅用于基本的连接测试和低速的数字电路测试

FT测试

英文全称Final Test,是芯片出厂前的最后一道拦截。测试对象是针对封装好的chip,CP测试之后会进行封装,封装之后进行FT测试。可以用来检测封装厂的工艺水平。

FT测试一般分为两个步骤:1)自动测试设备(ATE)2)系统级别测试(SLT)—2是必须项,1一般小公司可能用不起。ATE测试一般只需要几秒钟;SLT一般需要几个小时,逻辑比较简单。

FT的难点是如何在最短的时间内保证出厂的Unit能够完成全部的功能。FT需要tester(ATE)+ handler + socket。

a. 测试对象,封装后的芯片;

b. 测试目的,筛选,然后决定芯片可用做产品卖给客户。

c. 需要保证:spec指明的全部功能都要验证到。

WAT(Wafer Acception Test) 管芯结构性测试

晶圆生产出来后,在出晶圆厂之前,要经过一道电性测试,称为晶圆可接受度测试(WAT)。这个测试是测试在切割道(Scribe Line)上的测试键(TestKey)的电性能。测试键通常设计有各种原件,例如不同尺寸的NMOS、PMOS、电阻、电容以及其他工艺相关的特性。这一道可以当做是初选。那些有严重生产问题从而使得测试键的电性能超出规格之外的晶圆会在这一道被筛选出来,报废掉。这一道报废掉的晶圆,因为还没有出货到客户手里,所以是不收取客户钱的,由晶圆厂自己吸收。

对象:专门的测试图形的测试,结构测试。

目的:通过电参数监控wafer工艺各阶段是否正常和稳定。

没有回复内容