一根一根走线嫌慢?

那就多根线一起走

解决方案:

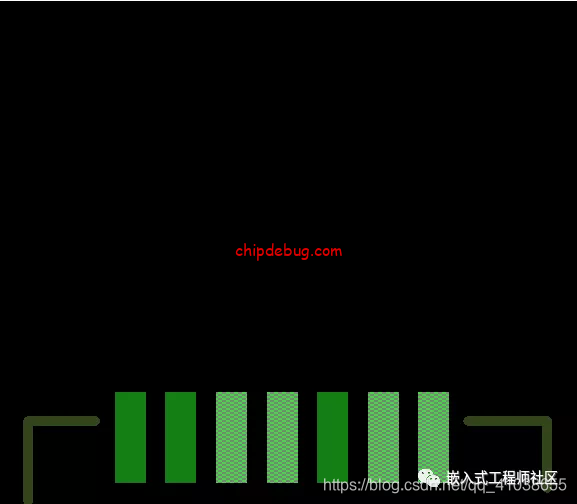

单击 Add Connect 图标

如果几个走线是相邻的

可以直接框选

如果不相邻

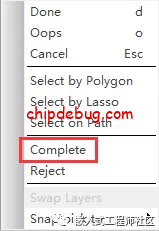

右键

选择 Temp Group

依次点击想要同时走线的焊盘

选择完后

右键

选择Complete

选中的网络同时拉出

其实也可以直接框选

其实也可以直接框选

还可以设置各个走线之间的线距

更换主控制线

转换为单线模式

设置线间距

走线过程中

右键

选择Route Spacing

弹出 Route Spacing 对话框

选中User defined

在space选项中直接设置线宽

各走线之间间距

自动设置为Route Spacing对话框中设定的值

点击OK关闭对话框

更换主控制线

主控制线是带X的走线

走线过程中

右键

选择Change Control Trace

单击作为主控制线的焊盘

可以看到主控制线已经更换

转换为单线模式

走线过程中

右键

选择Single Trace Mode

作为控制线的走线就会单独拉出来

其他的走线不再跟随

如果走完某根线后

还有其他的走线需要单独处理

在Single Trace Mode下右键

选择Change Control Trace

即可单独处理其他走线

处理结束后,右键

去掉勾选Single Trace Mode

恢复到群组走线

![图片[6]-Allegro-群组走线-PCB设计社区-FPGA CPLD-ChipDebug](http://5b0988e595225.cdn.sohucs.com/images/20200115/bc8d3c46f0134a61aa422c6f96885c16.JPG)

![图片[7]-Allegro-群组走线-PCB设计社区-FPGA CPLD-ChipDebug](http://5b0988e595225.cdn.sohucs.com/images/20200115/c4cc90fce45944e4bd1b147c9218c21e.JPG)

![图片[8]-Allegro-群组走线-PCB设计社区-FPGA CPLD-ChipDebug](http://5b0988e595225.cdn.sohucs.com/images/20200115/dd864d2ca3cd48c888eacc23e58a36c6.JPG)

![图片[9]-Allegro-群组走线-PCB设计社区-FPGA CPLD-ChipDebug](http://5b0988e595225.cdn.sohucs.com/images/20200115/e6de6d2883ce4ee78d07473f57a4c84e.JPG)

![图片[10]-Allegro-群组走线-PCB设计社区-FPGA CPLD-ChipDebug](http://5b0988e595225.cdn.sohucs.com/images/20200115/74f23ff1463b471b9bdc398f37419bcb.JPG)

![图片[11]-Allegro-群组走线-PCB设计社区-FPGA CPLD-ChipDebug](http://5b0988e595225.cdn.sohucs.com/images/20200115/1c9b9816d4a94b6690d5bd9391945db1.JPG)

没有回复内容