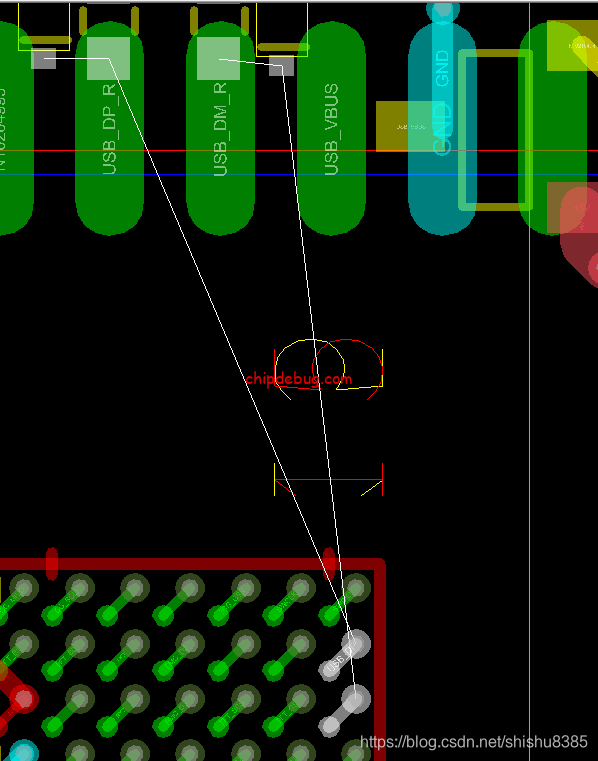

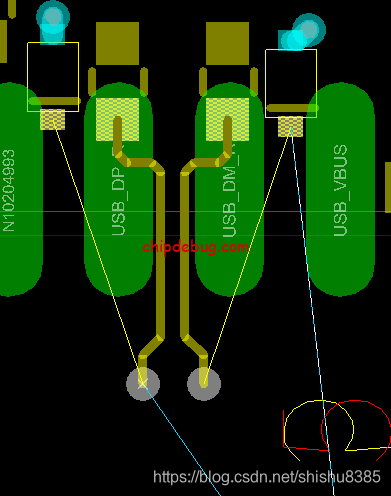

一般,遇到这种差分线不在一层的,需要换层的,就需要使用neck,neck的设置,见上一篇。如下图:底层的pin和top层的pin,需要连接在一起,这样,底层的需要走neck,top的走原有的设置。

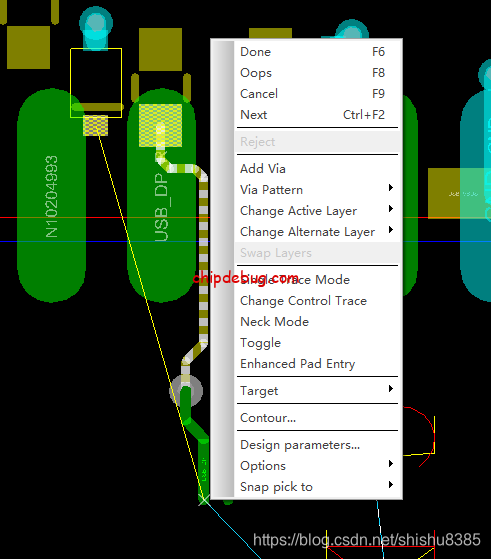

第一步:拉出差分线,右键,选择 neck mode模式

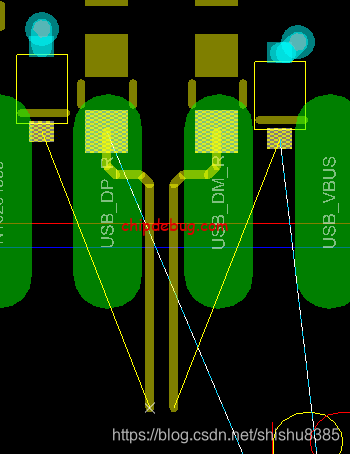

第二步:拉线,可以看出,确实走线变细了

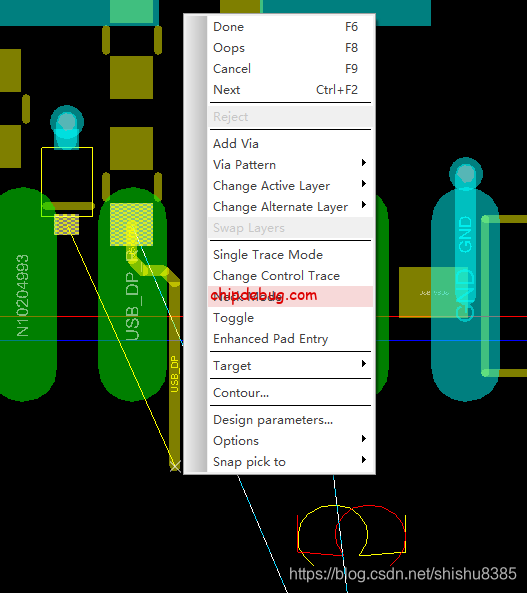

第三步,第三步,还是右键,选择过孔,以及过孔的样式:

第四步,选择过孔之后的效果:

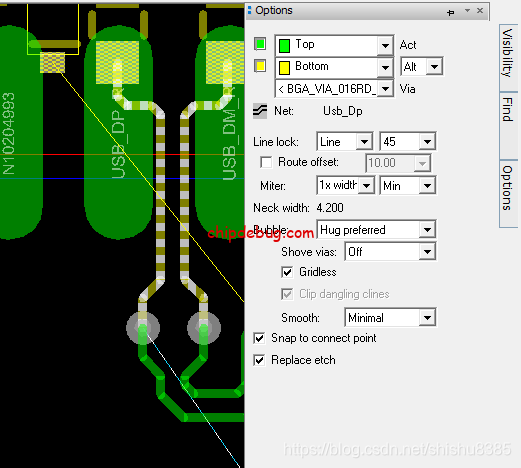

第五步:选择完过孔后,选择在option中,切换回来要换的层,top层

第六步:此时,还是右键,此时把 neck mode去掉,可以看出,top层走线,确实比底层走线宽了。

完毕。

cadence17.4 allegro的瓶颈模式走线

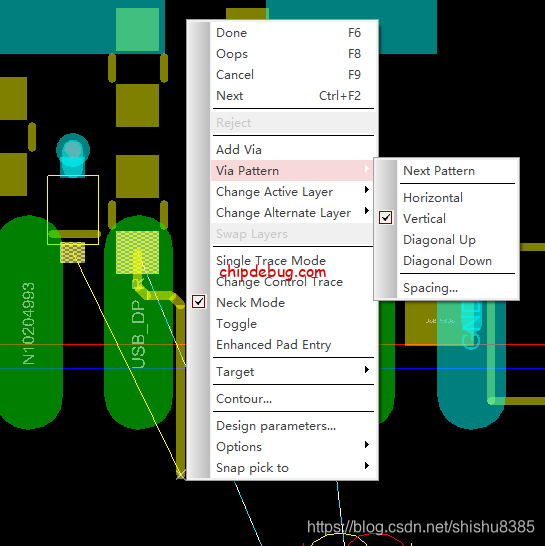

在某些场景下,BGA封装下密度比较大,走线的线宽可能不一致,当我们只设置另外一种走线线宽时,出现更细的走线会报错,而大多出的走线都是粗一些的,那么可以利用allegro的瓶颈走线模式来走线。

首先打开规则管理器的物理规则设置,设置线宽最小是5mil ,第二线宽时4mil。

回到PCB设计界面,当走线走到需要缩小线宽的地方时,选择Neck Mode模式走线即可。

效果图如下

没有回复内容