最近看到关于Anti Etch的设置,因为本人之前在layout设计是使用过这个命令。后来去到别的公司就不用了,从网上看到说这个命令是用来负片设计的。在这里在说下正片和负片的概念:

正片:是指在allegro中的走线和覆铜区域;

负片:Anti Etch是指allegro中的走线和覆铜区域,有Anti Etch是没有覆铜的;

其实大家可以根据自己的习惯利用Anti Etch,可以来设计负片,也可以用来分割电源层(因为有的电源高电压和低电压之间要保持一定的间距)。

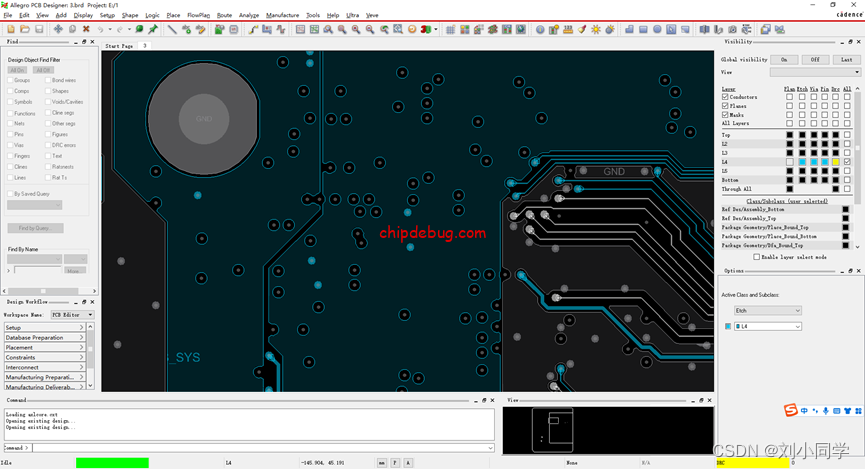

1.首先找到我们分割的电源或者地平面,从下图的电源平面的可以看到,两个电源网络之间的间距有的地方宽,有的地方窄,为保持间距一致性,就可以使用Anti Etch来分割平面:

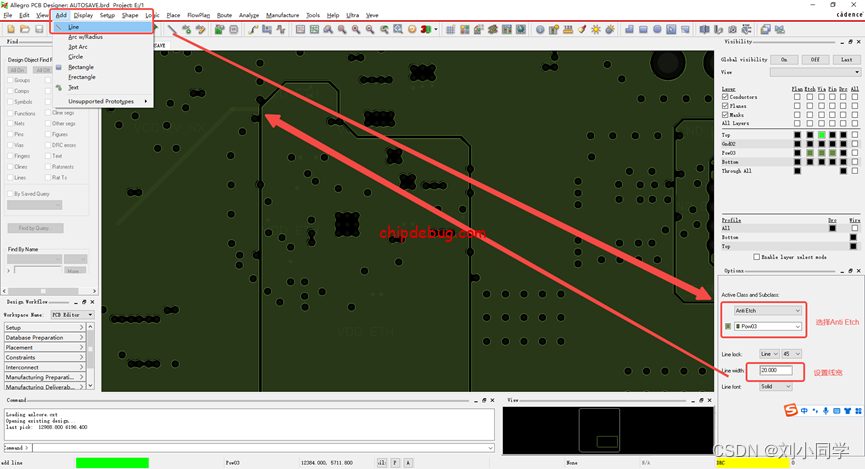

2. 在Allegro的菜单下选择Add命令,点击line命令。在活动层选择Anti Etch下面的电源层,设置好线宽如下图所示:

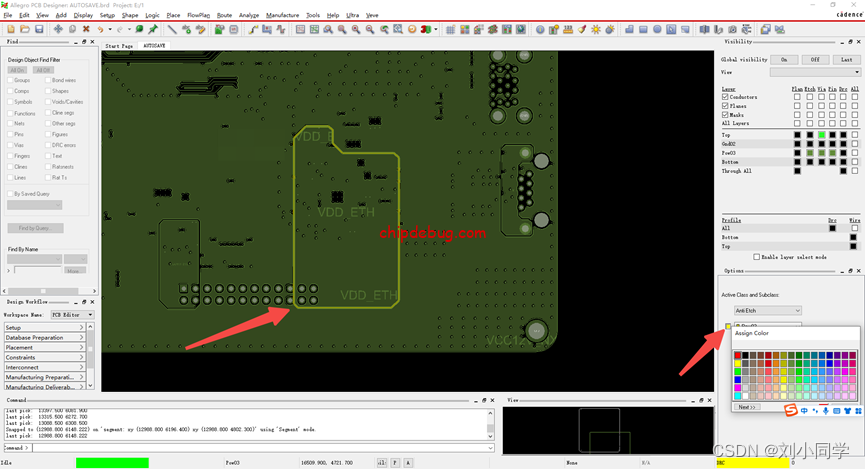

3. 按照电源的形状,画好Anti Etch,可以右键层级的颜色选择与电源层不同的颜色,方便查看:

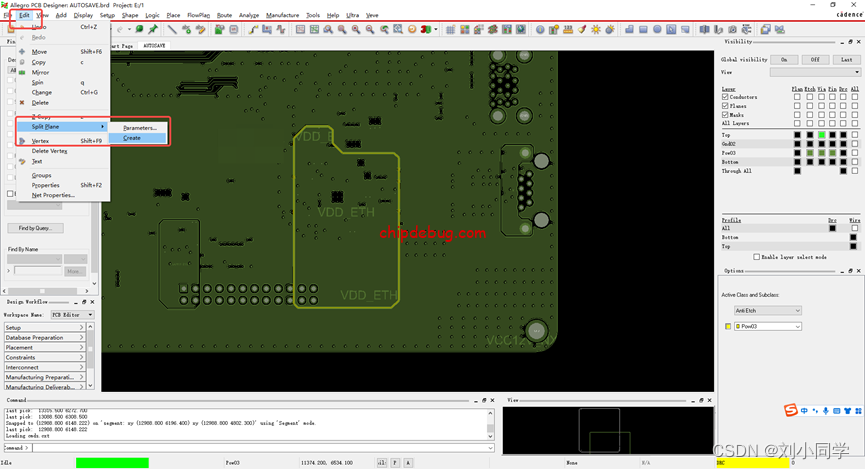

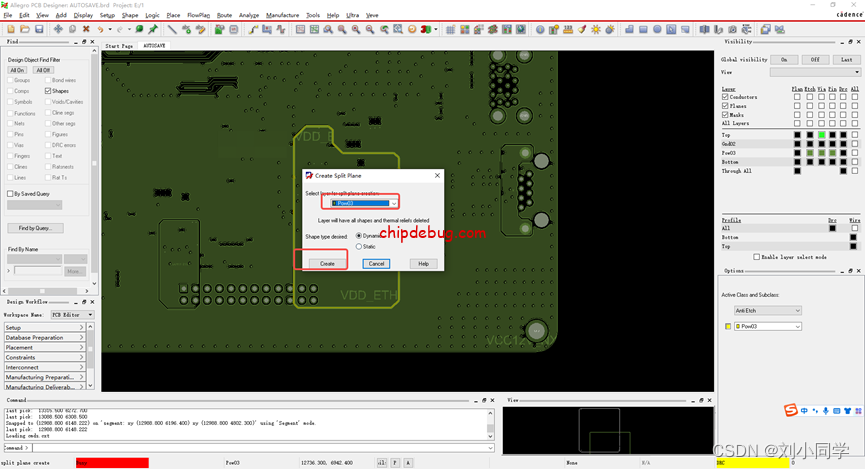

4. 在Allegro的菜单下选择Edit命令,点击split plane命令中的create,如下图所示

选择要分隔的平面:

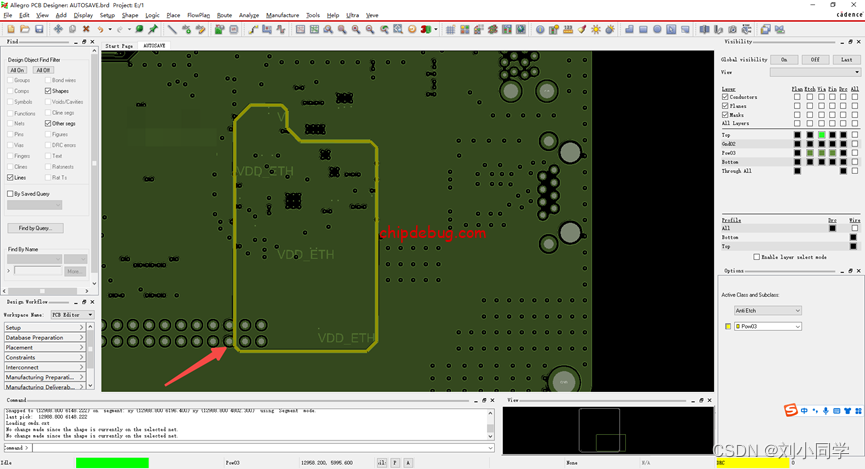

按照步骤以此选择分割的电源,最后点击OK即可,可以看到分割好的电源间距是按照之前设计的20mil,如下图所示:

没有回复内容