在项目的设计过程中会经常增加或者减少器件,到最后,图中的元件位号通常都不连续,这样很不利于调试,而且位号经常会变成多位,在后期调整PCB丝印时会占用很多空间。如果从原理图修改位号导入到PCB会导致器件直接飞掉。所以在设计完成时,重新对PCB板上的器件进行标号,然后再反馈到对应原理图上,使得原理图与PCB板的期间标号保持一致,这就是所谓的“反标”。

在Allegro软件中提供了”Rename”功能,可以为PCB板上的元件自动分配位号,分配规则可以设定。最常见的规则是从左到右,从上到下,依次命名。这样按照PCB布局重排位号后,可以让PCB的丝印标识更清晰,容易检查,位号易找,方便维修等。

第一步:反标原理

反标的全过程是这样的:在PCB板上对器件重新标号后会在项目所在文件夹PCB目录下生成rename文件(rename记录着标号的全过程和标号的结果),我们从该文件中取出重新标号的结果,再利用原理图软件把原理图中的器件照着rename文件中的结果一一对应进行标号,从而实现了原理图和PCB板的一致。

第二部:反标步骤

1、对PCB进行反标

①所有器件反标

如果想一次性把所有的器件都反标完成,执行Logic/Auto Rename Refdes/Rename命令,进入到下图界面,选择Rename all components对所有的器件反标,然后点击More进行设置,而我们只需对框选的部分参数进行设置,其余的参数为默认即可。

Preserve current prefixes打上勾表示保护前缀,把T和B去掉表示丝印中不加T和B。设置完成后点击Close,回到上一界面再点击Rename开始反标,完成后保存Rename文件。

②某一类器件反标

反标如果我们不同时反标所有器件,而是想对某一类别的器件反标呢?这种方式相对于第一种方式要复杂点,现在以反标电阻为例讲一下这种反标方法。执行Logic/Auto Rename RefDes/Rename进入到Rename界面,不选择Rename all components后,就可以点击Attach property components,然后在Find栏中点击More,我们只对Comp进行操作,如下图所示,找出所有的电阻。

此时会弹出下图窗口,单击Auto_Rename。

窗口右边出现Auto_Rename属性,单击Apply,右边器件属性中出现Auto_Rename属性,如上图。点击ok,关闭窗口。回到Rename界面,点击More进行反标参数设置,如下图所示,其余参数按照默认即可。

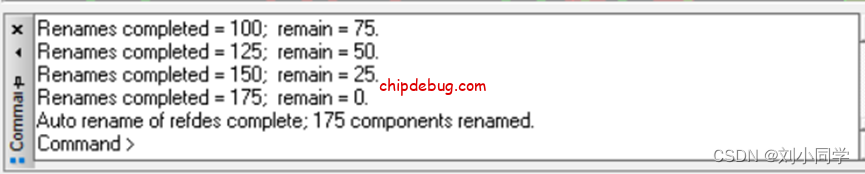

设置完成后点击Close,关闭窗口,回到上一界面再点击Rename开始反标,完成后命令窗口会出现如下图所示的log信息,此时rename成功。

回到PCB文件目录会出现下图所示的.log文件。每完成一次反标操作一定要及时保存rename.log文件,因为进行下一次反标的时候会覆盖上一次的文件。

2、Rename文件的处理

接下来说一下Rename文件的处理。Rename之后,PCB上元件的位号被改变。原理图与PCB上的元件命名不再一致。为了使原理图与PCB保持一致,必须把位号反标回原理图,也就是BackAnnotate。

打开得到的.log文件,如下图。

将文件中的所有“OLD ** NEW **”的语句复制出来,粘贴另一个记事本中。将OLD和NEW替换为空格,并且在开头加上“.Labels GateAndPinSwap”,在结尾加上“.End”。如下图所示。

最后,将文件另存为.swp格式的文件。

3、回标到原理图

打开原理图工程文件,如下图。先选择工程名,再点击tools-Back Annotate。

在弹出的页面进行如下设置,选择上一步保存好的.swp文件,点击确定即可。

此时,Allegro软件从PCB器件位号反标回原理图的操作全部完成,为了保证操作正确,可以导出网表到PCB文件验证一下。

没有回复内容