一、串扰仿真

以下Ansys SIwave 和Cadence Sigrity的串扰仿真操作流程,Cadence Sigrity 用到的组件是Power SI 和SPEED2000。可以在时域和频域两个角度来查看串扰的数据,话不多说,上图:

1.Ansys SIwave 串扰的时域和频域仿真

(一)Ansys SIwave 串扰的时域仿真

下面我们按照SIwave提供的流程指导进行仿真设置:

1.首先通过ANSYS Electronics Desktop软件来把brd文件导入SIwave中。

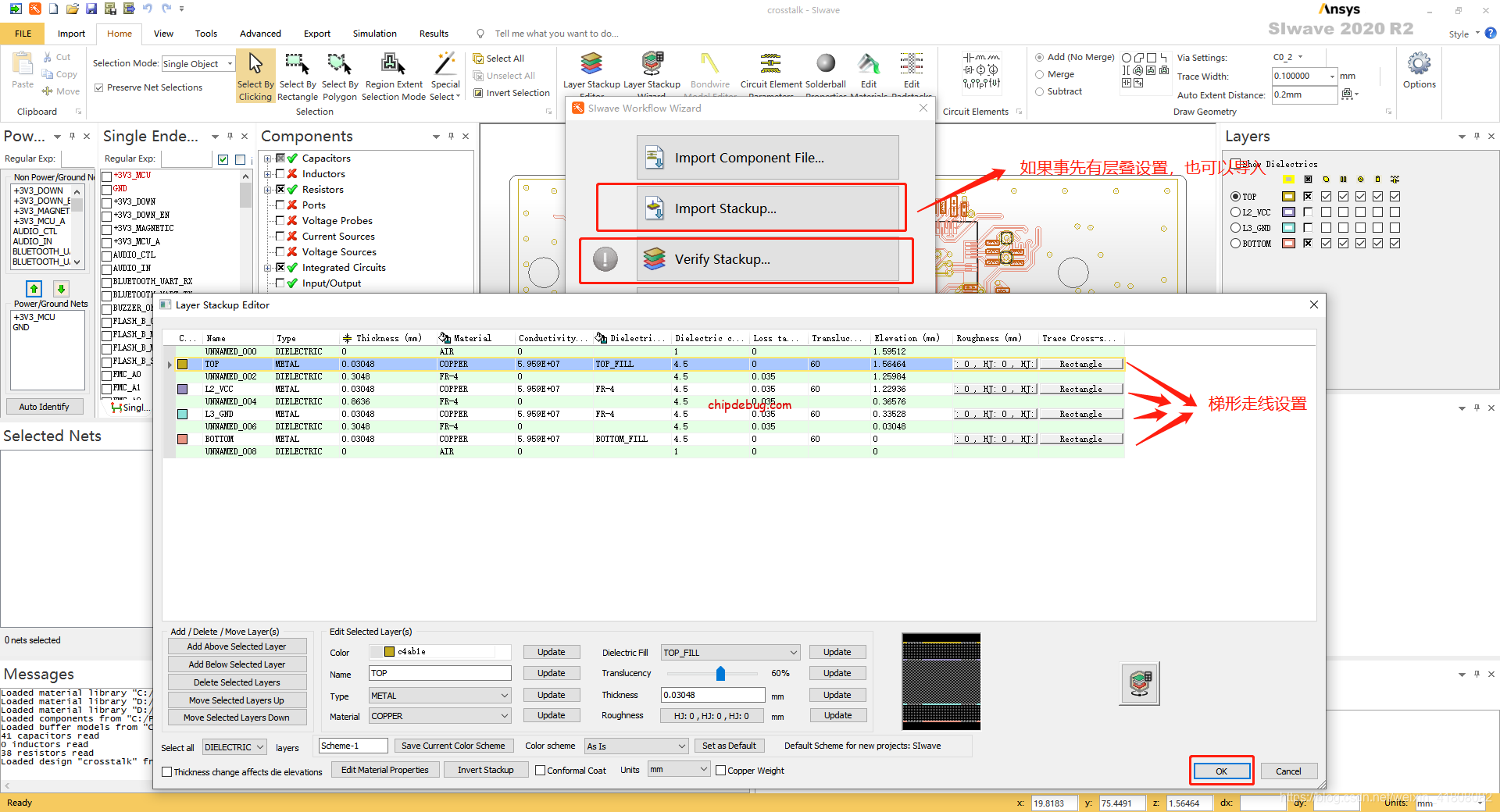

2.根据向导设置完成仿真,如下图:

3. 点击Verify Stackup,进行叠层设计(每层的厚度、材料、DkDf、铜的粗糙度、微带线的形状等,也可以自己新增材料),如下图:

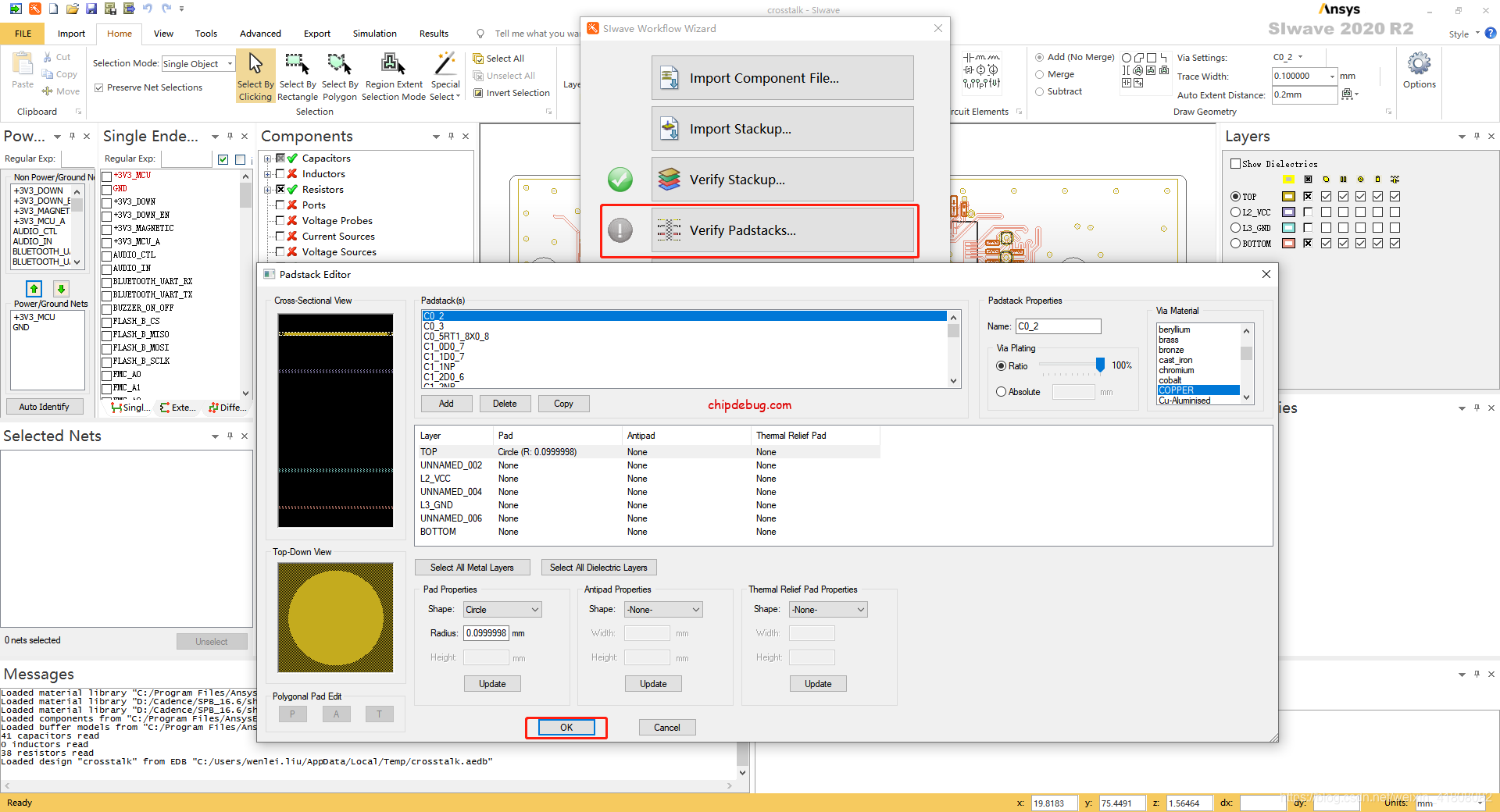

4.点击Verify Padstacks,进行焊盘和过孔设计(包括过孔的镀铜厚度等),如下图:

4. 点击Verify Circuit Element Parameters,阻容感器件是否被使能,如下图:

5.点击Verify Power/Ground Net Classification,把GND、POWER网络和其他网络分开,如下图:

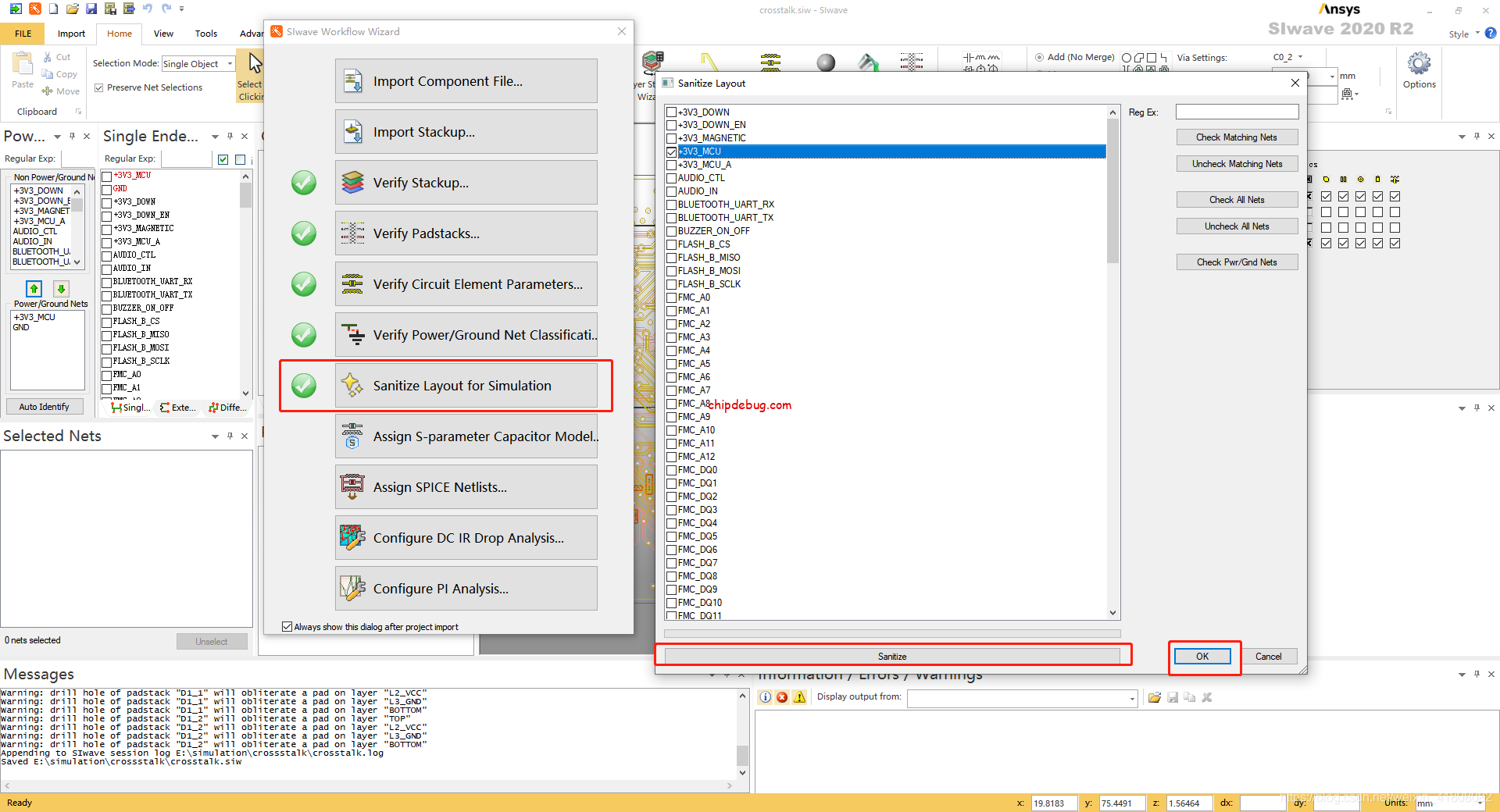

6. 点击Sanitize Layout for Simulation将文件中的重复的电源和地平面删除掉,如下图:

7. 点击Assign S-parameter Capacitor Model添加电容赋值(这个步骤在串扰仿真中可以不设置,但是在电源和其他的仿真中需要给电容赋值,所以我建议还是按照SIwave的向导设置好),如下图:

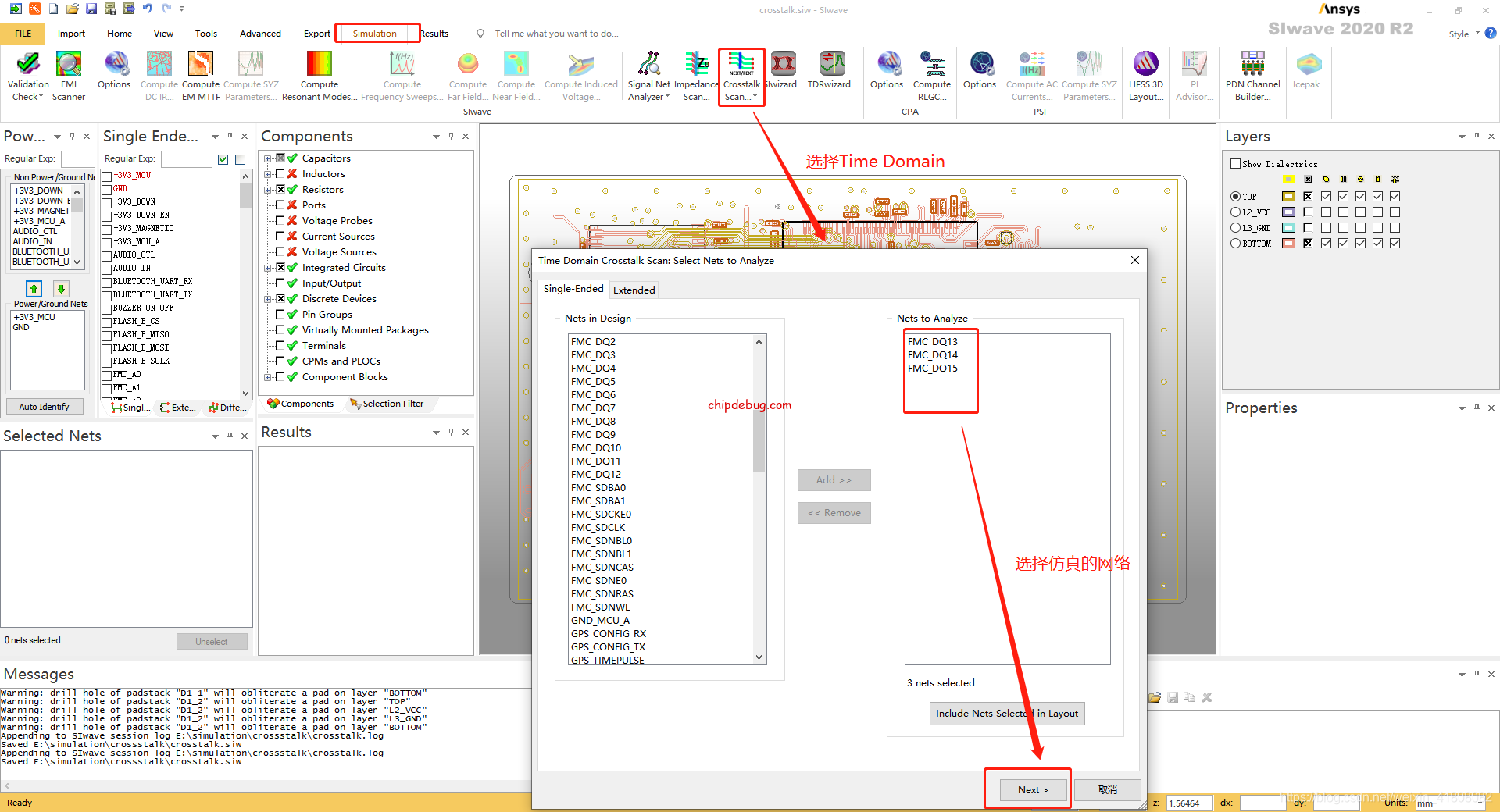

8.进行时域仿真设置,如下图:

9.仿真参数设置,如下图:

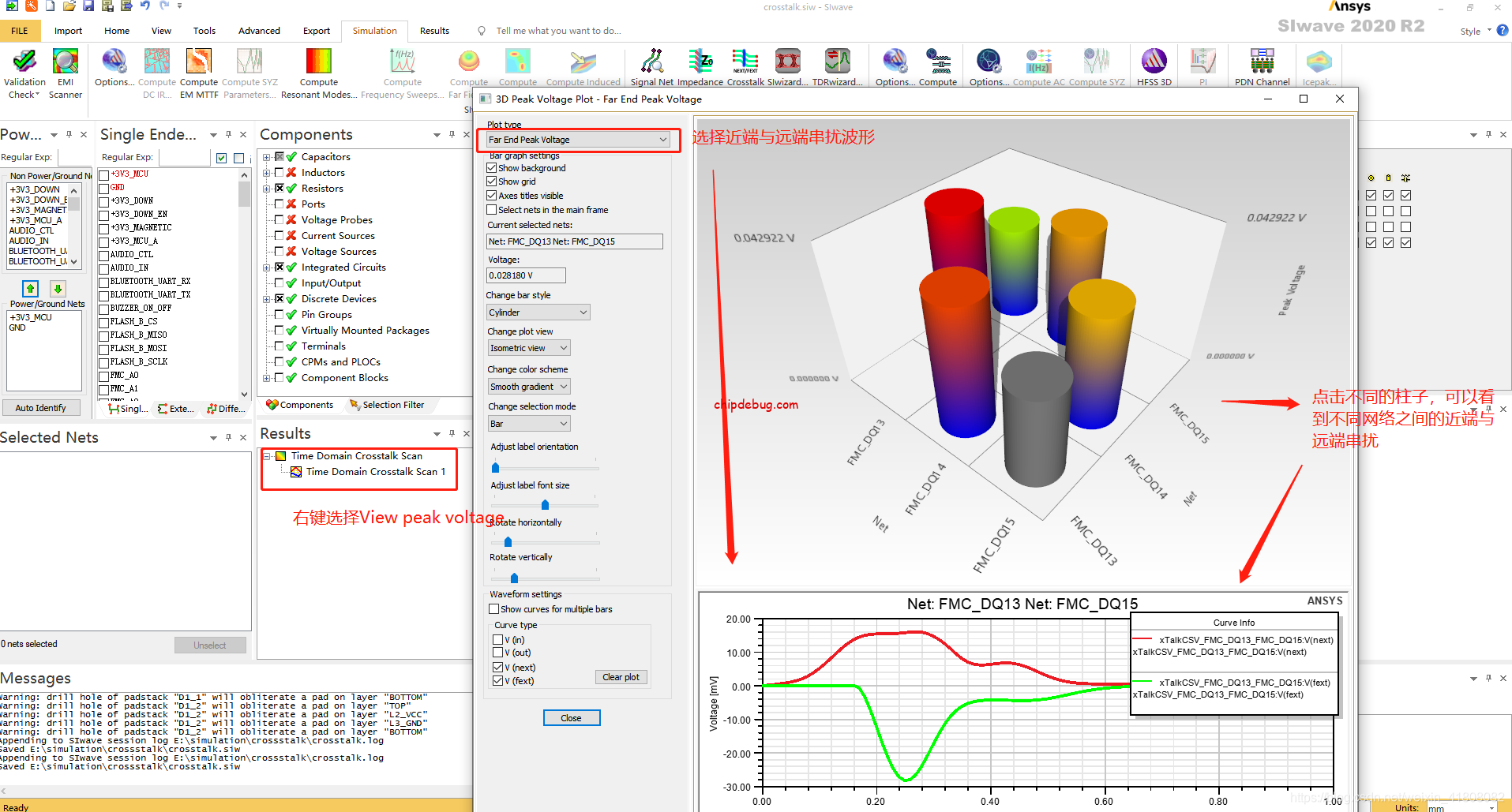

10.查看仿真结果,如下图:

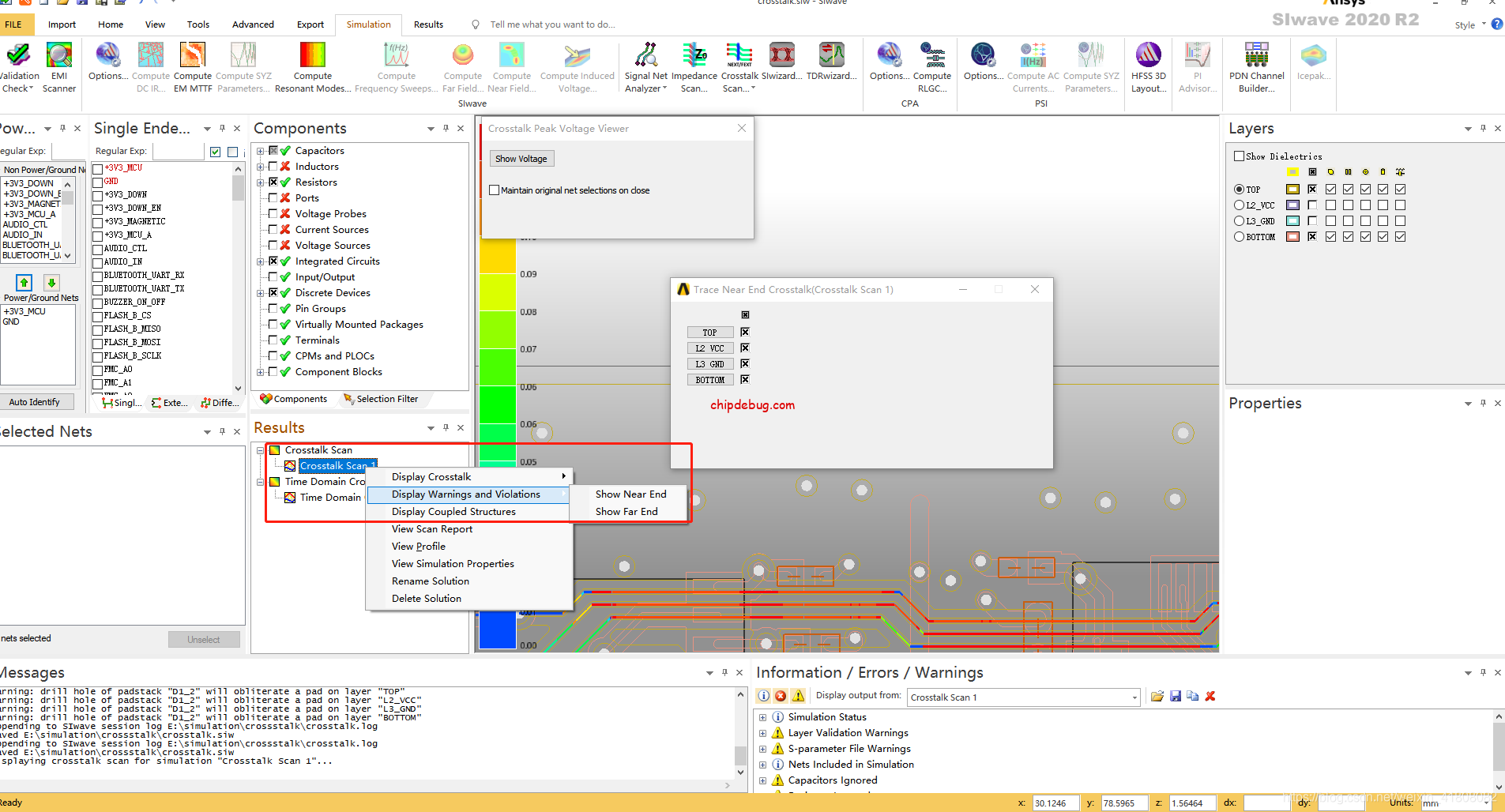

(二)Ansys SIwave 串扰的频域仿真

频域仿真的操作流程基本和时域的一样,只是在Cross Talk Scan 中选择Frequency Domain,设置如下图:

仿真结果查看,可以看到近端与远端的走线的耦合程度等,根据自己大家的想要的结果方式进行查看。

以上是Ansys SIwave的串扰仿真操作流程,感谢大家浏览观看,如果有不对的地方,还请大家指正。

动动小手点赞?关注欧,感谢!!!

没有回复内容