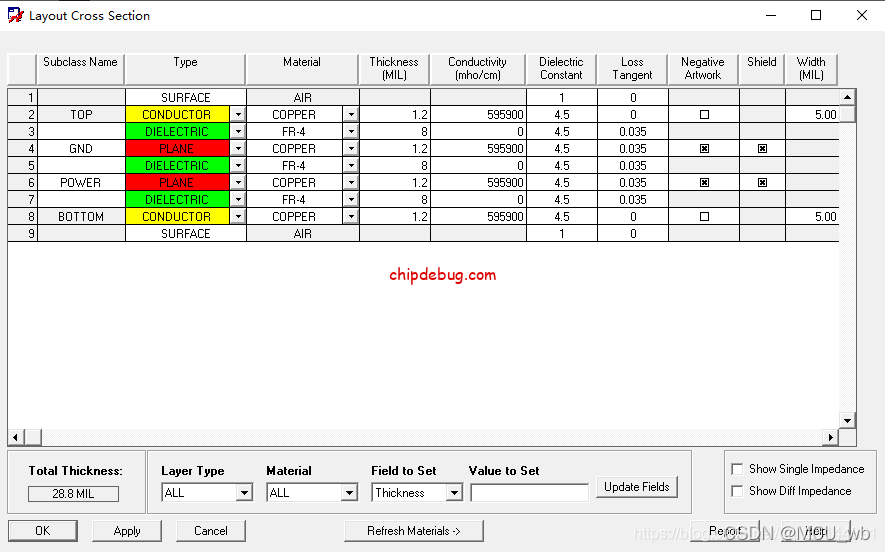

1.执行Setup-Cross-section命令,如图所示

**Subclass Name:**是该层的名称,可以按照自己的需要来填写。

**Type :**选择该层的类型,有三种:

(·**CONDUCTOR:**走线层;·**PLANE:**平面层,如GND平面;·**DIELECTRIC:**介电层,即隔离层。)

Material :设置的是该层的材料,一般根据实际PCB板厂提供的资料来设置。

(·COPPER:铜皮 ; ·FR – 4:玻璃纤维)

**Thickness :**设置的是该层的厚度,如果是走线层和平面层则是铜皮的厚度。

**Conductivtl:**设置的是铜皮的电阻率。

Dielectric Constant:设置介电层的介电常,与Thickness列的参数一起都是计算阻抗的必要参数。

**Loss Tangent:**设置介电层的正切损耗。

**Negtive Artwork:**设置的是该层是否以负片形式输出底片,(若勾上,则设置为负片;反之,为正片。

Apply / OK ,保存退出

关于Allegro层叠设置中plane和conduct区别解析

以此叠层结构做详细说明:

- Dielectric:绝缘体,不导电的,层间的介质选择这种属性;

- Conductor:导电介质,导电的,PCB信号层选择这种属性;

- PLANE:导电介质,导电的,PCB平面层选择这种属性。

Conductor与PLANE区别解析:

1、都是导电介质,都可以用于走线、铺铜、平面分割;2、方便PCB设计,区分走线层与平面层,生产出来的菲林都是一致的,生产出来的菲林都是一致的;

3、设计层叠时候,这里可以选择Conductor与PLANE属性,都是可以的,重要的是区分正负片,在Negative Artwork进行选择;

4、为了设计的规范性,一般建议是信号走线层设置成Conductor,平面层设置成PLANE;

5、为保证电源以及信号的完整性,信号层参考平面层做阻抗设计,平面层铺完整的铜,不走线,保证平面完整性,提供信号完整的参考面

没有回复内容