前言

试了一下芯片扇出的功能,现在不想要扇出了,照着线索试了一下,可以。

实验

先扇出一下

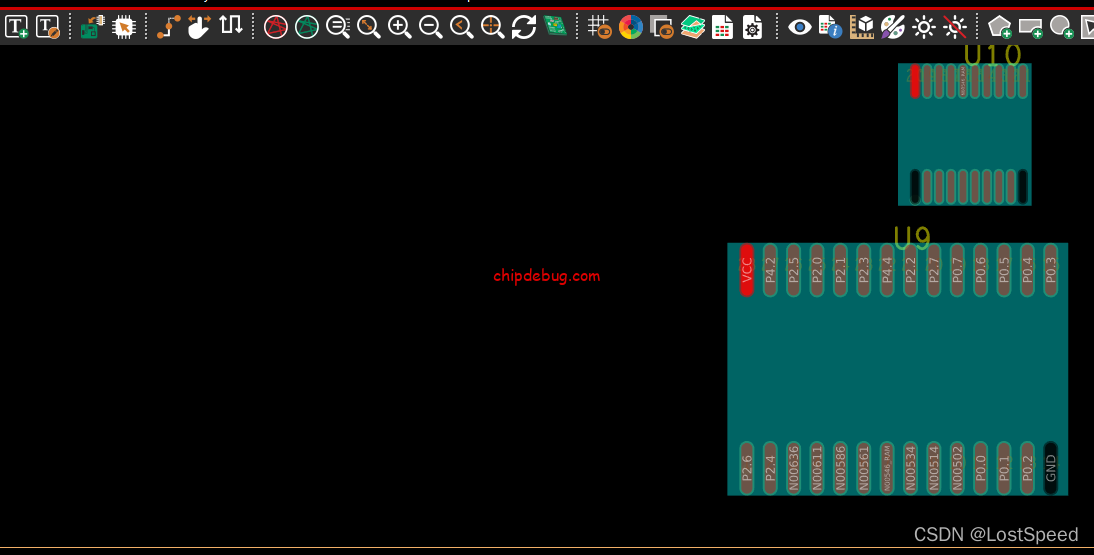

扇出后的芯片样子

扇出之后,等于是一个芯片的引脚引出了一个过孔。

现在只要选择芯片,扇出就会跟着芯片一起走。等于是一体的。

假设由于某种原因不想要扇出了。e.g. 扇出的焊盘规格没选合适,扇出方式不想按照BGA规则来扇出,或者我想自己拉线和放焊盘。

取消已经存在的芯片扇出

切换到放置编辑方式,这样取消扇出时,可以连续操作,方便。

在未选择任何器件时,从菜单上选择unmark

在右面板的find页选择pin, 其他去掉

将鼠标挪到芯片的引脚上,如果这个引脚是扇出状态,就会高亮,说明是可以操作的对象。

此时在可以高亮的引脚上左击,然后鼠标移动到其他可以高亮的引脚上继续左击,直到取消所有引脚的扇出绑定。

点击一下, 就执行了一个引脚的unmark, 左下角的命令窗口有提示,unmark成功。

芯片所有引脚都unmark后, 右击菜单完成unmark操作。

在find页只选中元件,然后左击拖动芯片到其他位置。可以看到扇出焊盘已经和芯片解绑了。

将操作方式切成普通编辑方式,准备删除解绑的扇出焊盘和扇出走线。

在Find页选择过孔和电气连线。

选中解绑的扇出孔和扇出连线,选择删除。

删除之后,只剩下了芯片,扇出元素删除的很干净。

END

超级版主

超级版主