RV-LINK:JTAG 接口和时序

JTAG 接口和时序在 IEEE 1149.1 中定义,可以在 CSDN 下载站 搜索下载。

接口

| 引脚 | 作用 |

|---|---|

| TCK | 时钟,上升沿捕获输入,下降沿变更输出 |

| TMS | 状态选择,仿真器在 TCK 下降沿输出,被测芯片在 TCK 上升沿捕获 |

| TDI | 串行数据输入,仿真器在 TCK 下降沿输出,被测芯片在 TCK 上升沿捕获 |

| TDO | 串行数据输出,被测芯片在 TCK 下降沿输出,仿真器在 TCK 上升沿捕获 |

TCK 应接下拉电阻,按照 IEEE 1149.1 的要求,被测芯片在 TCK 保持低电平的情况下将保持原有的状态,所以 TCK 应该拉低,确保在没有接仿真器时 TCK 是低电平状态。

TMS 应接上拉电阻,根据 TAP 状态机,任意状态下,只要 TMS 保持高电平 5 个时钟,那么就会进入复位状态,所以 TMS 拉高是安全的。

时序

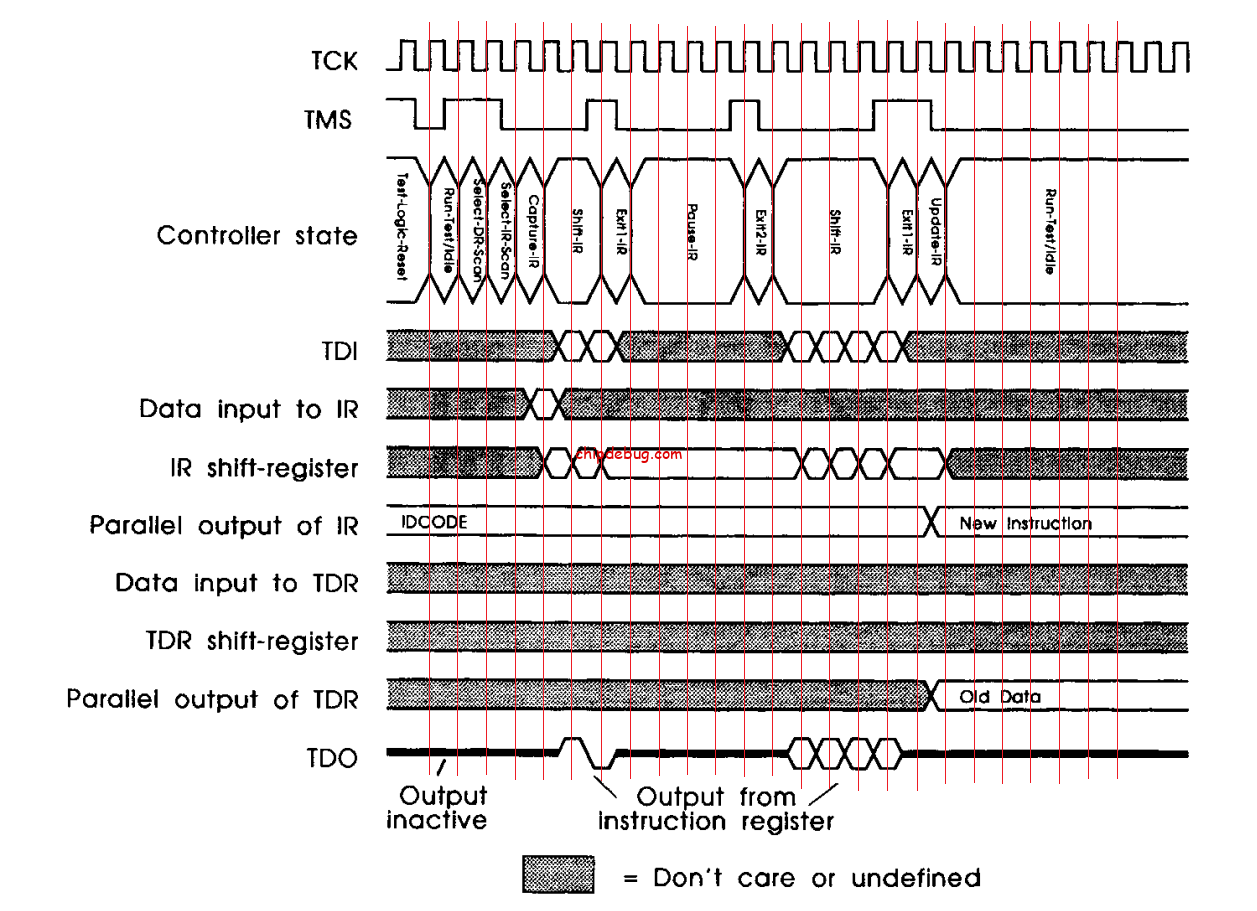

指令寄存器扫描

下图从 IEEE 1149.1 文档中截图,为了便于查看,添加了红色栅格线。

从时序图可以清晰地看出,仿真器在 TCK 下降沿改变 TMS、TDI 电平,被测芯片在 TCK 上升沿捕获输入并更新内部状态。被测芯片在 TCK 下降沿改变 TDO 电平,仿真器在 TCK 上升沿捕获 TDO 数据。

需要特别注意的是:最后一位数据是在进入 Exit1-IR 状态的那个上升沿捕获的,数据寄存器也同样存在这个特点。

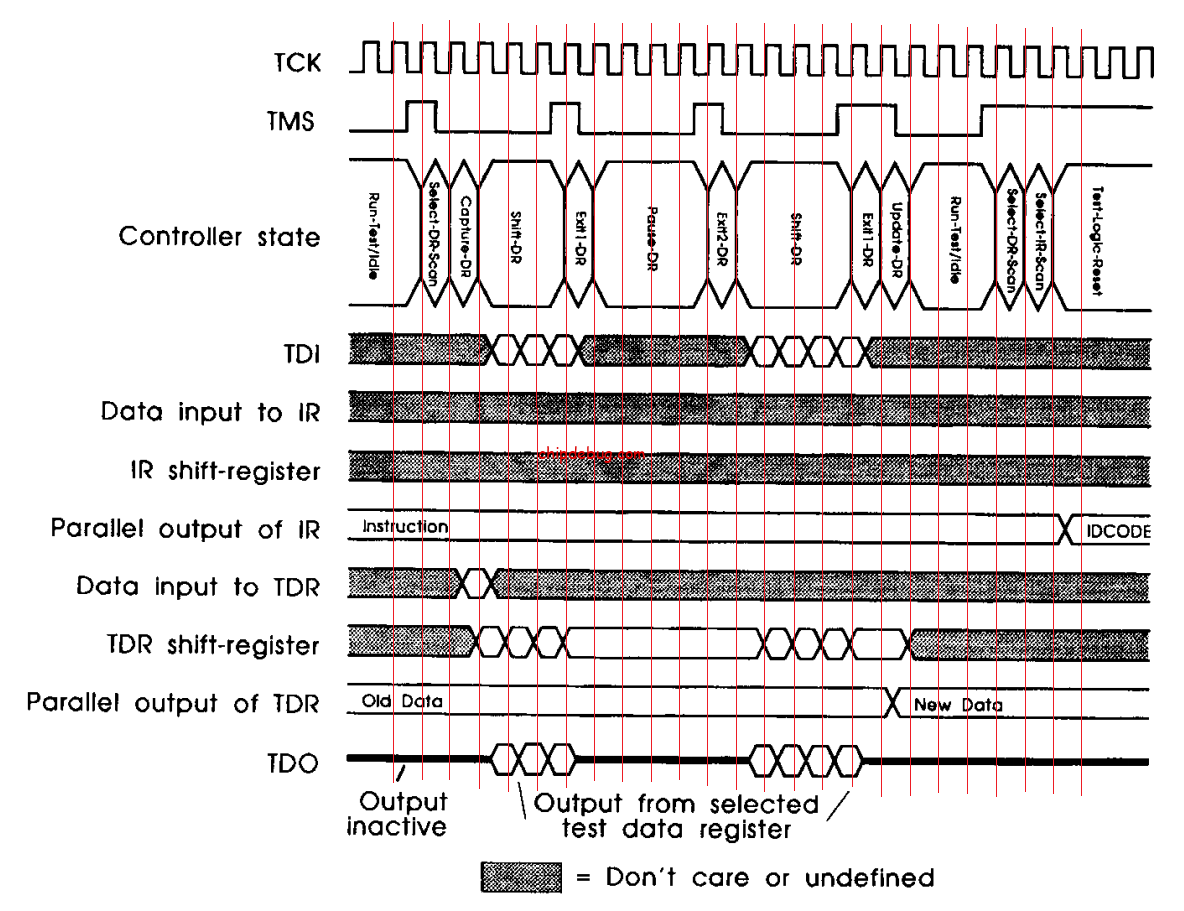

数据寄存器扫描

下图从 IEEE 1149.1 文档中截图,为了便于查看,添加了红色栅格线。

RV-LINK 的实现

TCK 周期驱动

rvl_tap_tick 函数执行一个 TCK 周期,四个阶段:低电平半周期、上升沿、高电平半周期、下降沿。

int rvl_tap_tick(int tms, int tdi) { int tdo; /* * ___ * ___| | */ // 1. 低电平半周期,首先输出 TMS、TDI 然后延时半个周期 rvl_jtag_tms_put(tms); rvl_jtag_tdi_put(tdi); rvl_jtag_delay_half_period(); // 2. 上升沿,上升沿之后读取 TDO rvl_jtag_tck_put(1); tdo = rvl_jtag_tdo_get(); // 3. 高电平半周期 rvl_jtag_delay_half_period(); // 4. 下降沿 rvl_jtag_tck_put(0); return tdo; } 实测波形

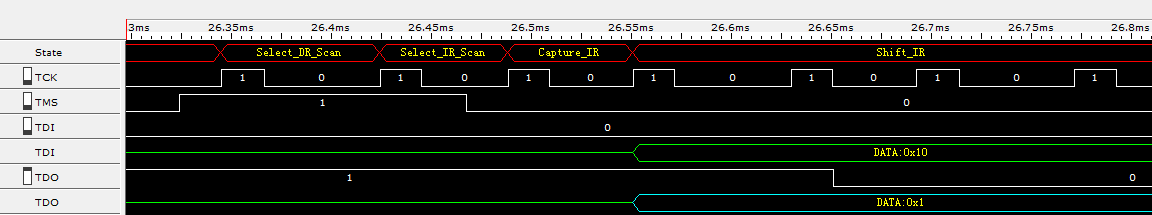

读取 id 和 dtmcs 的完整波形 IR 扫描的波形

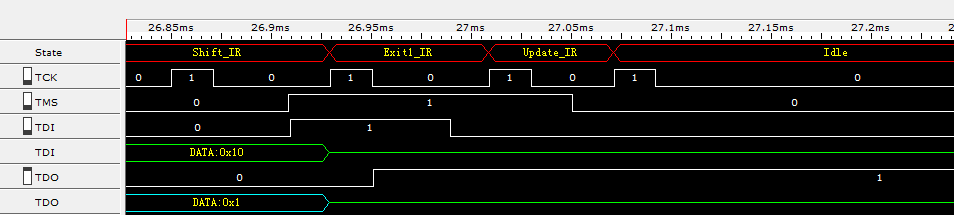

IR 扫描的波形 DR 扫描的波形

DR 扫描的波形

进入 Shift-IR 状态的细节

进入 Shift-IR 状态的细节

退出 Shift-IR 状态的细节

实测电路

没有回复内容