之所以把物理层电气部分的文章放在链路初始化与训练文章的后面,是因为这一部分涉及到一些相关的概念,如Beacon Signal、LTSSM等等。

前面已经多次提及,由于本次连载的文章主要是基于Gen2的,所以关于Gen3的相关内容只会提及,但是并不会深入的介绍,如果有兴趣的可以自行阅读Gen3的Spec。

关于链路初始化与训练的文章中提到过,PCIe Spec规定,支持新的标准的PCIe设备应当能够向前兼容。即Gen2的设备必须同时支持2.5GT/s和5GT/s。

注:当然这也不是绝对的,当摸一个设备只支持5GT/s速率时,可以通过将Link Capability 2 Reg中的Supported Link Speed 置为全0,同时将Link Control 2 Reg中的Hardware Autonomous Speed Disable置1。来禁止系统尝试将速率降为2.5GT/s。

PCIe Spec规定,PCIe设备必须是Short-Circuit Tolerant的,这可以让PCIe卡支持热插拔的功能。此外,由于PCIe总线是一种高速的差分总线,因此,其收发两端是交流耦合的(AC-Coupled)。一般情况下,靠近发送端的链路上放置电容来滤除直流信号,如下图所示:

详细的差分收发对模型如下图所示:

当然,如果PCIe设备把电容集成到Silicon(芯片)中,也是可以的(不过一般不会这么做,因为在芯片内部集成大电容成本很高)。使用交流耦合的另一个优势是,可以允许链路两端的设备使用不同的电源和地。

注:关于半导体中的电容,以及芯片周围的一堆退耦电容是什么鬼,打算找个时间单独写一篇文章来详细地聊一聊。

注:关于PCIe的热插拔实现机制,后续单独写一篇文章来介绍。有兴趣的读者也可自行阅读PCIe Card Spec的相关章节。

需要注意的是,PCIe总线采用的是嵌入式时钟,即只有数据Lane,并没有时钟Lane(对于Gen1/Gen2,是通过8b/10b编码来嵌入和恢复时钟的;对于Gen3及之后的版本,是通过扰码和128b/130b来实现嵌入和恢复时钟的)。

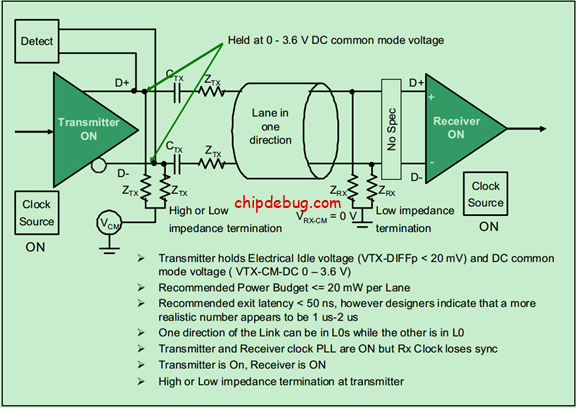

L0模式下的链路结构图(状态图)如下:

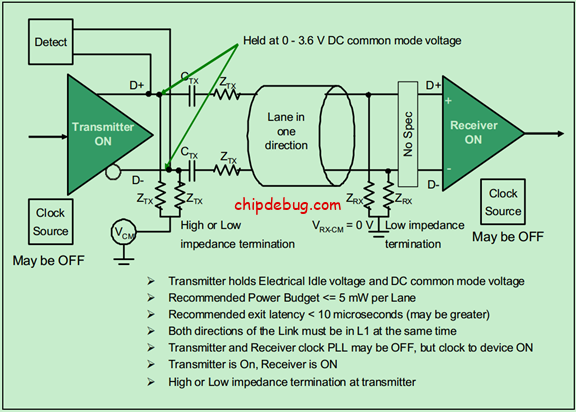

L0s模式下的链路结构图(状态图)如下:

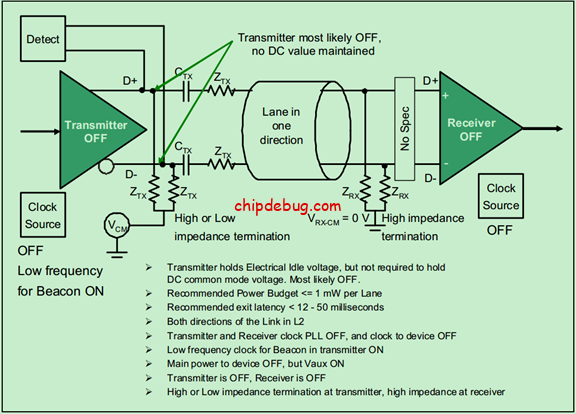

L1模式下的链路结构图(状态图)如下:

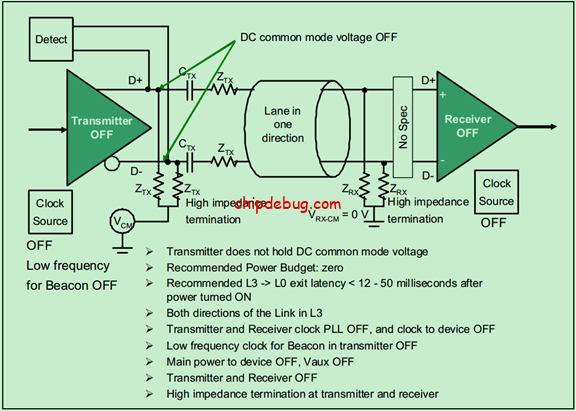

L2模式的链路结构图(状态图)如下:

L3模式的链路结构图(状态图)如下:

没有回复内容