前面的文章介绍过,PCIe总线除了有Base Spec,还有关于PCIe卡的Spec(又称为CEM Spec,全称为PCI Express Card Electromechanical Specification)。该Spec主要内容包括辅助信号(Auxiliary Signals)、热插拔(Add-in Card Hot Insertion and Removal)、电源传递(Power Delivery)、PCIe卡电气规范(Add-in Card Electrical Budget)、连接器规范(Connector Specification)和PCIe卡的外形与尺寸规范(Card Form Factors and Implementation)等。

注:除了标准的PCIe Add-in卡之外,还有一种PCIe Riser卡,主要用于将一个PCIe插槽扩展为多个PCIe插槽。如下图所示:

其中关于PCIe卡的热插拔功能,已经在前面的文章中介绍过,这里就不在重复了。本文主要介绍的是辅助信号与电源传递等相关内容。如需了解其他内容,还请阅读相关的CEM Spec或者相关书籍。

注:这里说的辅助信号(Auxiliary Signals)主要是针对于PCIe卡的,而非PCIe的On-Board连接。

PCIe卡的辅助信号主要有:

※ REFCLK(Reference Clock,参考时钟),【must be supplied by system】

※ PRSNT1# & PRSNT2#(Add-in Card Presence Detect Pins),【Required】

※ PERST# 【Required】

※ JTAG(调试引脚),【Optional】

※ SMBus(System Management Bus,基于I2C的),【Optional】

※ WAKE#(用于链路唤醒的功能,一般建议使用),【Optional】

※ +3.3V Vaux(3.3V的辅助电源),【Optional】

PCIe卡的REFCLK是一种类LVDS信号(即Low Voltage Swing,Differential Clocks),其单端摆幅为0~0.7V,时钟频率为100MHz,精度为±300ppm。对于支持扩频时钟(Spread Spectrum Clocking,一种降低系统EMI的手段)的系统,正向综合精度为300ppm+2500ppm=2800ppm。即-300ppm~2800ppm。REFCLK的详细DC Spec和AC Timing要求如下表所示:

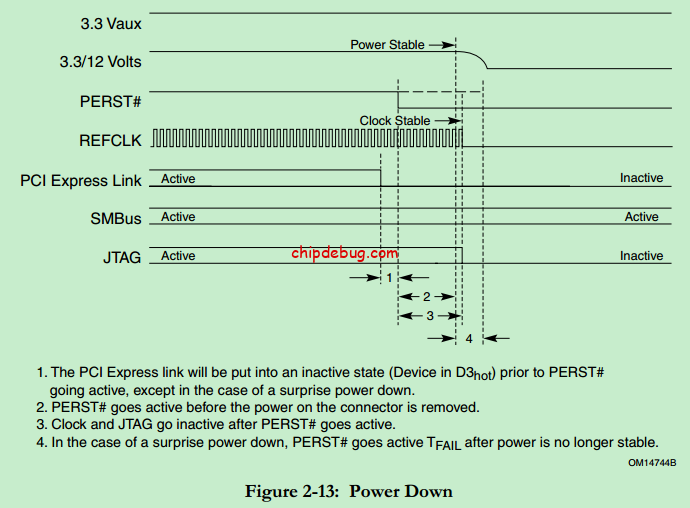

PCIe卡的各个信号有效状态与PM State的关系图,如以下三张图所示:

WAKE#信号是一种开漏(Open Drain)结构,低电平有效的信号。主要用于唤醒插槽上的主电源和参考时钟等,进而唤醒链路(Links)。需要注意的是,WAKE#信号的电平变换操作与任何系统时钟都是异步的(Asynchronous)。

注:WAKE#和PME#是两码事,WAKE#不可以被直接连接到PME#信号上。PCI-PME#往往会产生中断信号,而WAKE#只是用于唤醒操作,一般并不会直接产生中断。

PCIe卡至少需要有两个电源:+12V和+3.3V,第三个辅助电源+3.3Vaux是可选的。各个电源的基本要求如下:

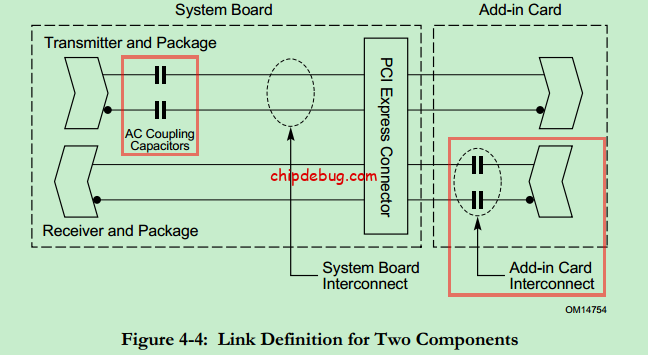

由于PCIe是一种高速串行总线,因此其链路上的信号线基本上采用的都是交流耦合(AC Coupling),也就是在传输线上加上一个电容,以过滤掉直流和低频信号。PCIe CEM Spec建议,一般将交流耦合的电容放置于发送端,如下图所示:

![正在上传... 图片[7]-PCIe扫盲——PCIe卡Spec(CEM)导读-FPGA CPLD资料源码分享社区-FPGA CPLD-ChipDebug](http://chipdebug.com/wp-content/uploads/2022/10/41665282592.gif)

注:其他的信息(如Jitter,Equalization、Skew、Trace Impedance等电气信息;眼图;连接器与PCIe卡外形;信号完整性基本要求与测试流程等)将不再详细介绍,如需了解,请自行阅读PCIe CEM SPec。

附:PCIe卡的Pinout信息:

没有回复内容