自2019年下半年,PCIe Gen5正式发布以来,其单个Lane/Channel速率已达32Gbps,传统的FR4电路板支持这么高的速率是完全不可能的事情。即使面对的是Gen4带来的16Gbps,FR4仍在瑟瑟发抖……

在6GT/s以下的串行通信协议中,8B/10B编码的是绝对的主流,其完美的DC均衡编码,极大地降低了串行收发器(尤其是Receiver)的设计难度。但是8B/10B的浪费20%带宽的缺点,限制了其在6GT/s以上速率串行协议中的进一步演进……于是各种高效率编码开始出现,如Ethernet 10GBASE-R PCS中用的64B/66B,PCIe Gen3及以上版本用的128B/130B,DisplayPort用的128B/132B,64B/67B……等等

新的高效率编码,借助更加复杂的扰码器,依然可以实现较长时间内的直流均衡,但是不可避免地会带来更长的Run Length(数据流中连续的0或者1)。这对串行接收器(Receiver)提出了更高的要求,往往也需要更加复杂的CDR设计,匹配以更加复杂的Tx/Rx EQ手段。

然而,相比于每提高1Gbps速率所需要的硬件成本(更低损耗的板材,价格是传统FR4的数倍),使用高效率编码带来的成本显然更低。

以PCIe应用来说,PCIe Gen3 仍可以较为容易地在普通的FR4上实现。但是Gen4则需要比FR4更低损耗的板材,这也是为什么支持PCIe Gen4的PC主板要比不支持Gen4的贵很多的原因之一。然而,即使是使用更贵(低损耗)的板材,长距离地传输16Gbps的信号仍然是一个非常大的挑战。在PCIe Gen4 Base Spec,还首次提出了信号调节的概念。有两种信号调节功能的器件:

-

ReTimer,

-

ReDriver

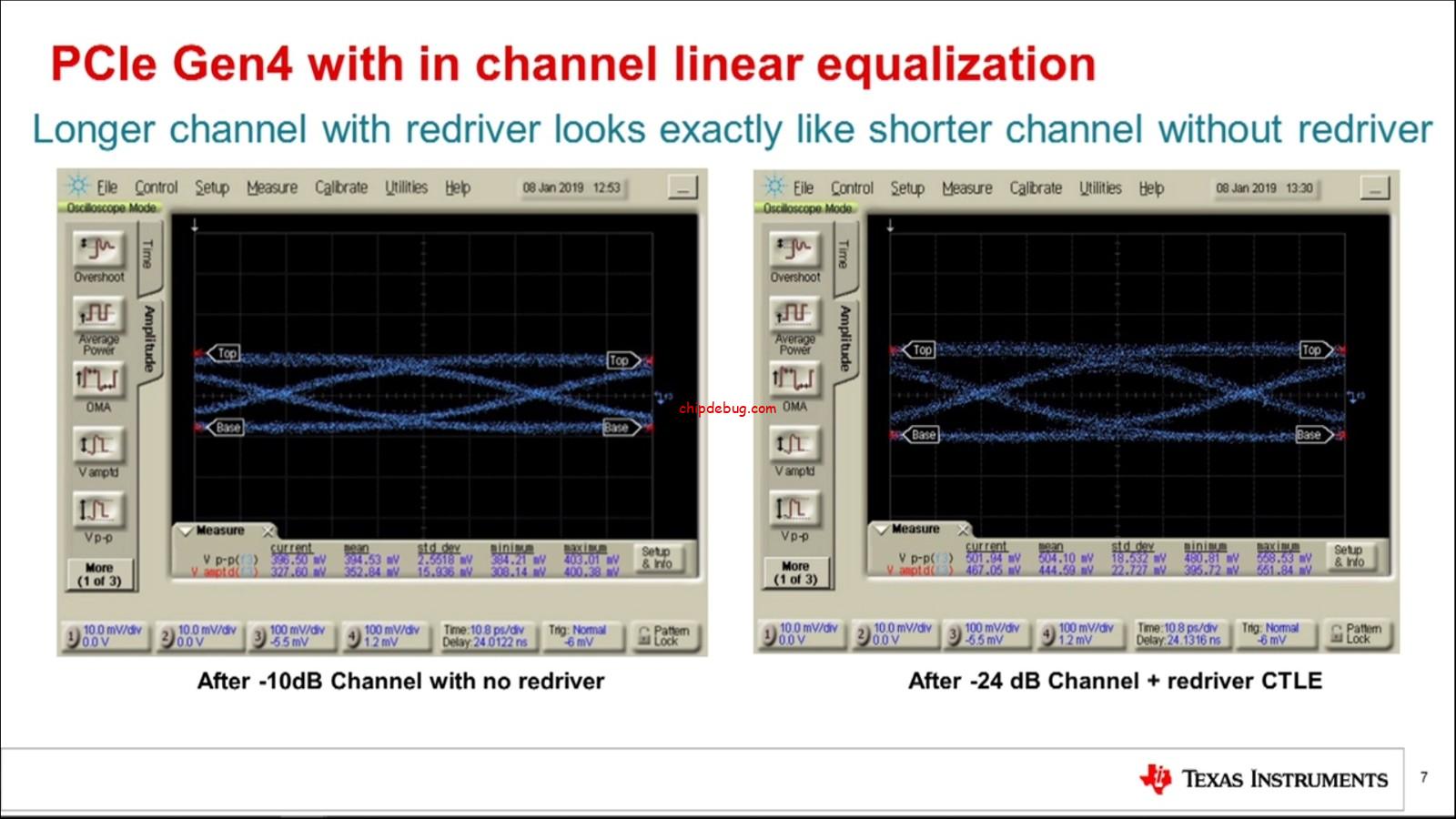

ReDriver功能相对简单,其通过Rx端的CTLE(基本原理一般就是一个高通滤波器),和Tx端的驱动器,实现对损耗的补偿,进而使得眼图的窗口变大,让整个PCIe通道看起来有更小的衰减。由于ReDriver有没涉及到任何协议相关的内容,所以其两端的PCIe设备是无法感知到ReDriver器件的存在的。

ReTimer不仅会在Rx端实现CTLE和DFE,还会在Tx端实现相应的EQ功能。这使得ReTimer器件能够分别于其两端的器件实现EQ Training,如上图所示。

因此ReTimer能够实现比ReDriver更好的降低通道物理损耗的效果。然而,复杂的ReTimer会增加更多的Latency。以PCIe Gen4应用为例,ReTimer带来的Latency可达64ns,而ReDriver往往只有100ps。

下面是几个使用ReTimer/ReDriver的例子:

注:本文主要参考资料来自TI,原文网址:https://edu.21ic.com/lesson/2217

没有回复内容