本文主要介绍Lattice近期发布的两款芯片对PCIe协议的支持,以及相关IP的使用方法和注意事项。

Lattice在19年底,发布了业界首款采用28nm FDSOI工艺的FPGA——CrossLink-NX,2020年又发布了基于同平台的Certus-NX。不过这两个产品区别主要在MIPI接口上,其他几乎是完全一样的,所以就直接放在一起讲了。用Lattice官方的说法,这个28nm FDSOI平台被命名为Lattice Nexus Platform,后续还会有其他的FPGA产品基于该平台构建。

FDSOI工艺相比于CMOS/FinFET工艺,功耗要低很多,引用官方发布的PPT数据,只有同级竞争对手的四分之一:在运行PCIe Gen2x1的设计时,只有200mW左右,远低于Xilinx Artix-7和Altera Cyclone V GT。

如果只计算PCIe SerDes/PMA的功耗的话,实测功耗只有96mW。

和早期的产品(ECP3/ECP5)不同的是,CrossLink-NX和Certus-NX中集成的是Hard Core。该Hard Core实际上可以支持PCIe Gen3x1,并向前兼容Gen2和Gen1。不过,由于CrossLink-NX和Certus-NX主要定位是超低功耗,FPGA内部逻辑支撑复杂的Gen3x1设计可能存在压力,保守起见暂时只支持Gen2x1。

Lattice提供了一个PCIe soft IP wrapper,其中实现了AMBA一些桥接功能和一个简单的DMA功能,但是似乎不太好用。用户可以选择AHB-Lite或者AXI4-Stream来替换默认的PCIe TLP接口,其中AXI4-Stream接口和Xilinx的PCIe IP几乎是一样的。但是Lattice提供的AHB-Lite就有点奇怪了:不支持单独的Master或者Slave接口(和AXI4-Stream一样),如果需要DMA功能,则会有两个AHB-Lite Master接口,一个只管接收,一个只管发送……如果不需要DMA功能的话,同样需要两个AHB-Lite接口,其中Master只管接收,Slave只管发送……如下图所示:

所以……还不如直接使用Hard Core直接出来的TLP接口……

以下是使用TLP接口的一些注意事项:

1,有一些常用的信号,比如LTSSM状态、PM状态、Current Configuration ID都没有直接引出来,需要用户通过UCFG(Configuration Space Register Interface)接口去获取:

2,假设FPGA作为Endpoint,从FPGA往Root发送数据,用户需要先把数据放上去,然后等待ready信号变为有效,并且时刻注意ready信号的状态。因为如果选择等待ready信号变为有效之后再放数据,可能ready信号永远都不会变为有效……如下图所示:

3、对于简单的应用,用户可以直接通过ready信号来实现Flow Control,但是需要考虑类似如下这种情况:由于当前正在发送的MWr TLP比较大,对端的器件的Buffer放不下,这会导致ready信号一直处于无效状态知道对端器件释放出最够大的Buffer,但是对端的器件可能在等待我们的中断到来之后才释放Buffer。然而,中端走的是Message,是Posted类型与MWr属于同一类型,也就是说ready信号变为无效后,Message肯定是无法正常发送的,这会造成死循环……

针对这种情况,用户需要通过LMMI接口去访问Flow Control Credits相关的寄存器,来确定当前时刻对端器件是否有足够的Buffer,并保留一个Posted Header Credit给中断传输。

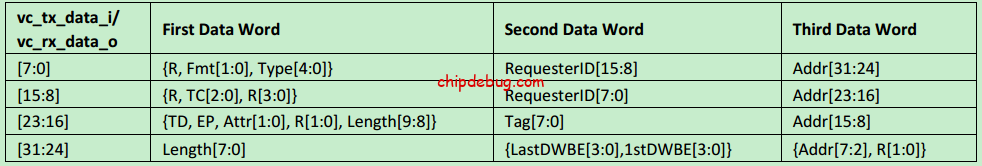

4、CrossLink-NX/Certus-NX的PCIe IP的数据次序(Data Byte Order)和ECP3/ECP5的Soft PCIe IP不同,具体请参考IPUG的相关章节,以32-bit的MRd包头为例:

更多内容,持续更新!

没有回复内容