简介

在当今高度集成的系统中,降噪是电路板设计人员的重中之重。带有嵌入式时钟的串行传输数据可以显着减少数据走线,并且无需在电路板上运行时钟走线。这最大限度地减少了电路板上的潜在串扰并提高了整个系统的信号完整性。

曼彻斯特编码是一种将数据和时钟组合成单个自同步数据流的方法,而曼彻斯特解码是从串行接收的数据流中检索时钟和数据。为了在不使用伴随时钟信号的情况下正确接收数据,必须对接收到的串行数据执行时钟和数据恢复 (CDR) 功能。锁相环 (PLL) 与过采样一起是一种常用于执行时钟数据恢复的技术。

差分曼彻斯特码是标准曼彻斯特码的替代品。两者都有其优势,并被用于不同的应用领域。共同的好处之一是编码数据流的直流分量电平为零。与标准曼彻斯特码相比,如果信号反转,差分曼彻斯特码将以相同的方式运行。

此参考设计提供了一个示例,说明如何使用差分曼彻斯特代码实现低速串行控制链路。它利用片上 PLL 对传入的串行数据流进行过采样。此应用使用过采样技术,因为控制链路通常以低于数据路径的速度运行。这与差分曼彻斯特码的特性一起,使得从串行数据中提取数据和时钟信息成为可能。

特征

• 差分曼彻斯特编码/解码

• 串行数据输入(接收通道)/串行数据输出(发送通道)

• 无需奇偶校验插入和检查

• 基于过采样技术的时钟恢复

• 由于编码信号的差分特性,无需前导码

功能说明

图 1 显示了此参考设计中实现的不同功能以及输入/输出信号的框图。

信号描述

倍频模块

差分曼彻斯特编码数据需要两个逻辑电平来表示每个二进制位,因此编码后的数据速率是输入数据速率的两倍。 基于此,差分曼彻斯特编码需要一个频率为输入串行数据速率两倍的时钟。

为了在接收端对串行数据流进行过采样,输入数据的每一位使用相位相差 90 度的两个时钟进行四次采样。 图 2 显示了本设计中使用的四次过采样概念。

倍频模块利用片上 PLL 根据本地参考时钟生成时钟 rx_clk 和 rx_clk_90。 时钟 rx_clk 和 rx_clk_90 的频率等同于输入串行数据速率。 每个代码位看到四个时钟边沿,这些时钟边沿依次提供四个采样数据点。 这相当于以比输入数据速率快四倍的时钟进行采样。

差分曼彻斯特编码

差分曼彻斯特编码需要一个频率是输入串行数据速率两倍的时钟。 在设计中,差分曼彻斯特编码定义如下:

• 每个位在固定时间(参考时钟的“周期”)内传输。

• 在位时间的开始总是有一个转换,无论是从高到低,还是从低到高。

• 通过使信号的前半部分等于信号的后半部分来指示“0”位。 也就是说,在位时间的中间没有转换。

• • 通过使信号的前半部分与信号的后半部分相反来指示“1”位。 也就是说,转换发生在位时间的中间。

图 3 显示了此参考设计中的差分曼彻斯特代码如何表示二进制值。

差分曼彻斯特解码和时钟恢复

该模块需要两个具有 90 度相位差的时钟,以与输入差分曼彻斯特码率相同的频率运行。输入数据的良好采样是采样时钟的建立时间和保持时间都可以满足。这通常发生在对位的中间进行采样时。根据数据位的到达和时钟相位,对位中间进行采样的边沿可能会有所不同。图 4 总结了使用不同时钟边沿来获得最佳样本的四种情况。以情况 2 为例,rx_clk_90 的上升沿首先看到数据位“a”。因此,由 rx_clk 的下降沿或 rx_clk_90 的下降沿采样的数据点可以被认为是数据位“a”的最佳表示。该理论与差分曼彻斯特码的特性一起,提供了每个数据位的准确采样和恢复。使用差分曼彻斯特码,在代码中间发生跳变时可以采样和恢复位“1”,在代码末尾发生跳变时可以采样和恢复位“0”。

由于 rx_clk 的频率等于输入数据码率,因此恢复的时钟频率是 rx_clk 频率的二分之一。时钟的相位信息嵌入在输入数据流的转换中。结果,在发生转变时检测到恢复时钟的相位。

Test Bench说明

此设计的Test Bench包括一个随机二进制信号发生器 (prbs_gen.v),它生成用于编码和解码的随机二进制信号。 在仿真过程中,bench 会在 testbench 子目录中创建两个文件:original_data.txt 和 recovery_data.txt。 第一个文件记录用于编码的原始数据,第二个文件记录由恢复时钟计时的恢复数据。

时序图

差分曼彻斯特编码

差分曼彻斯特解码

性能和资源占用

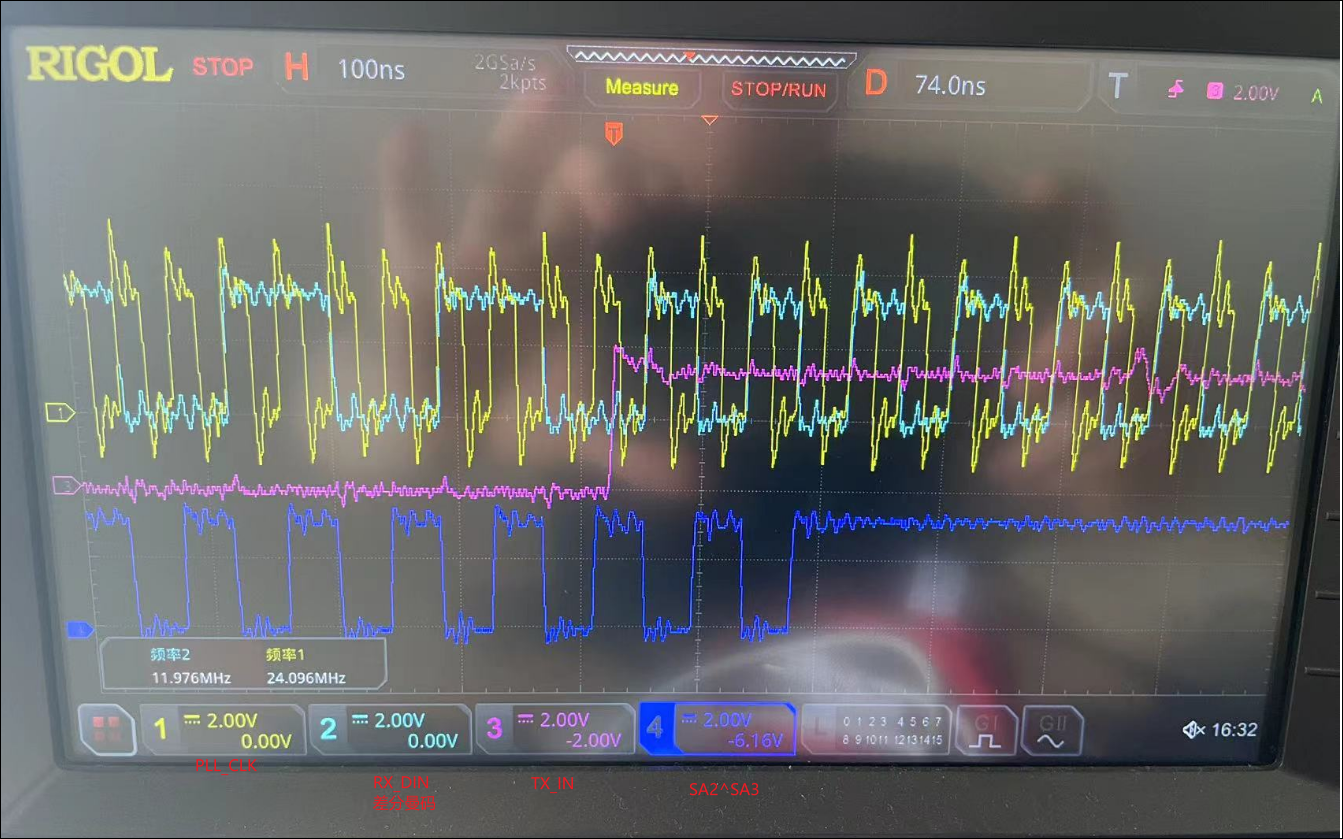

3、又用示波器捕获了一个在单个开发板上的测试,此测试中使用通道3做为编码输入进行触发。

3、又用示波器捕获了一个在单个开发板上的测试,此测试中使用通道3做为编码输入进行触发。

4、其于上面的原因,我怀疑问题可能还是取值这里,中间的延时赋值,好像没有生效,通过更改参数,不会能最后的编译结果造成改变。中间为什么这么进行取值,未理解。

4、其于上面的原因,我怀疑问题可能还是取值这里,中间的延时赋值,好像没有生效,通过更改参数,不会能最后的编译结果造成改变。中间为什么这么进行取值,未理解。